DATA SHEET

# ASSP for DTS Bi-CMOS 1.1 GHz PLL Frequency Synthesizer

# **MB15A01**

### **■ DESCRIPTION**

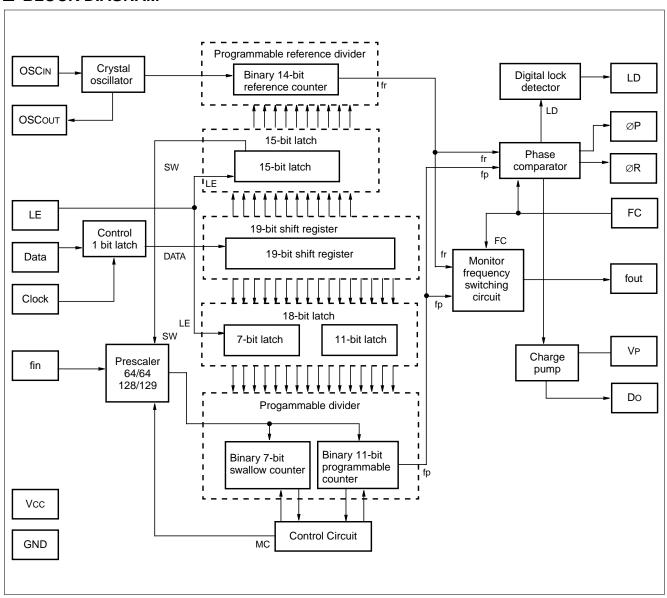

The MB15A01 is a serial-input PLL (phase locked loop) frequency synthesizer LSI supporting a pulse swallow system.

The LSI consists of: a 1.1 GHz band, dual-modulus prescaler allowing either of 64/65 and 128/129 frequency divisions to be selected, a control signal generator circuit, a 19-bit shift register, a 15-bit latch, a reference divider (binary 14-bit reference counter), a 1-bit switch counter, a phase comparator with phase conversion functions, a charge pump, a crystal oscillator, an 18-bit latch, and programmable dividers (binary 7-bit swallow counter and binary 11-bit programmable counter).

The LSI is housed in a 16-pin or 20-pin SSOP package, contributing to space saving of the system incorporating it. In addition, the MB15A01 operates at a low supply voltage of 3.0 V (typical), achieving low current consumption (typically Icc = 6.5 mA)

#### **■ FEATURES**

• Operation at high speed: fin = 1.1 GHz (Vin = -10 dBm)

Pulse swallow function: Internal dual-modulus prescaler allowing either of 64/65 and 128/129 frequency

divisions to be selected

• Low current consumption: Icc = 6.5 mA (typical)

(Continued)

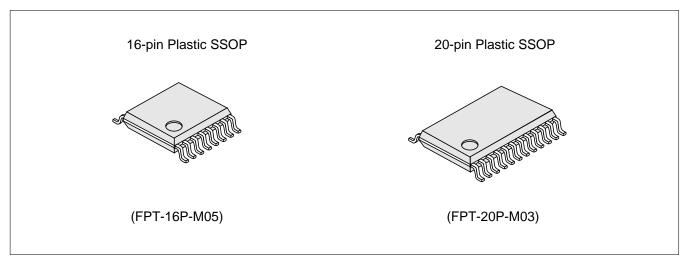

### ■ PACKAGES

### (Continued)

- Serial-input 18-bit programmable divider

Divide ratio of binary 7-bit swallow counter (0 to 127)

Binary 11-bit programmable counter (16 to 2,047)

- Serial-input 15-bit reference divider

Divide ratio of binary 14-bit programmable reference counter (6 to 16,383)

1-bit switch counter (for setting the prescaler divide ratio)

- Serial data configuration compatible with conventional models such as MB1511

- Two different phase comparator outputs Internal charge pump output (bipolar type) Output for external charge pump

- Wide range of operating temperature: Ta = -40 to +85°C

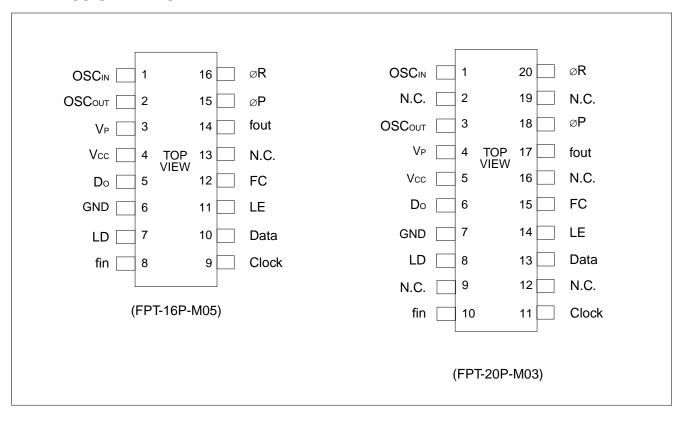

### **■ PIN ASSIGNMENTS**

### ■ PIN DESCRIPTION

| Pin No. |                     | <b>5</b> . |     | <b>-</b>                                                                                                                                                                                                  |  |  |  |

|---------|---------------------|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SSOP-16 | SSOP-20             | Pin name   | I/O | Function                                                                                                                                                                                                  |  |  |  |

| 1       | 1                   | OSCIN      | I   | Crystal oscillator connection pin serving as a reference divider inpupin (Oscillator circuit input pin)                                                                                                   |  |  |  |

| 2       | 3                   | ОSСоит     | 0   | Crystal oscillator connection pin (Oscillator circuit output pin)                                                                                                                                         |  |  |  |

| 3       | 4                   | VP         | _   | Power supply pin for charge pump output Connect this pin to Vcc when the internal charge pump is not used.                                                                                                |  |  |  |

| 4       | 5                   | Vcc        | _   | Power supply pin                                                                                                                                                                                          |  |  |  |

| 5       | 6                   | Do         | 0   | Internal charge pump output pin                                                                                                                                                                           |  |  |  |

| 6       | 7                   | GND        | _   | GND pin                                                                                                                                                                                                   |  |  |  |

| 7       | 8                   | LD         | 0   | Lock detector output pin When locked: LD = "H", When unlocked: LD = "L"                                                                                                                                   |  |  |  |

| 8       | 10                  | fin        | I   | Prescaler input pin The pin must be AC-coupled for input.                                                                                                                                                 |  |  |  |

| 9       | 11                  | Clock      | I   | Clock input pin for 19-bit and 16-bit shift registers The shift resistors reads data at the rise of the clock pulse.                                                                                      |  |  |  |

| 10      | 13                  | Data       | I   | Binary-coded serial data input pin The last bit in the data is a control bit. Control bit = "H": Sends data to the 15-bit latch. "L": Sends data to the 18-bit latch.                                     |  |  |  |

| 11      | 14                  | LE         | I   | Load enable signal input pin (with pull-up resistor) When LE = "H", the pin sends the contents of the shift register to the latch according to the control bit.                                           |  |  |  |

| 12      | 15                  | FC         | I   | Phase comparator phase switching pin (with pull-up resistor) When FC = "L", the pin inverts characteristics of the phase comparator. It also switches the fout pin (test pin) output between fr and fp.   |  |  |  |

| 13      | 2, 9, 12,<br>16, 19 | N.C.       | _   | No connection.                                                                                                                                                                                            |  |  |  |

| 14      | 17                  | fout       | 0   | Phase comparator input monitor pin The pin outputs the reference divider output (fr) or programmable divider output (fp) signal depending on the FC pin input level. It is a N channel open-drain output. |  |  |  |

| 15      | 18                  | øΡ         | 0   | Phase comparator output pin for external charge pump This pin is an N channel open-drain output.                                                                                                          |  |  |  |

| 16      | 20                  | øR         | 0   | Phase comparator output pin for external charge pump This pin is a CMOS output.                                                                                                                           |  |  |  |

### **■ BLOCK DIAGRAM**

### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol   | Rat         | ing       | Unit | Remarks |

|----------------------|----------|-------------|-----------|------|---------|

| Farameter            | Syllibol | Min.        | Max.      | Onit | Remarks |

| Power supply voltage | Vcc      | -0.5        | +5.0      | V    |         |

| Fower supply voltage | VP       | Vcc         | +8.0      | V    |         |

| Output voltage       | Vo       | -0.5        | Vcc + 0.5 | V    |         |

| Open-drain voltage   | Voop     | -0.5        | +6.0      | V    | øP pin  |

| Output current       | lo       | -10         | +10       | mA   |         |

| Storage temperature  | Tstg     | <b>–</b> 55 | +125      | °C   |         |

Precaution: Permanent device damage may occur if the above absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol |      | Unit |      |       |

|-----------------------|--------|------|------|------|-------|

| Farameter             | Symbol | Min. | Тур. | Max. | Offic |

| Dower ourphy voltage  | Vcc    | 2.7  | 3.0  | 3.5  | V     |

| Power supply voltage  | VP     | Vcc  | _    | 6.0  | V     |

| Input voltage         | Vı     | GND  | _    | Vcc  | V     |

| Operating temperature | Та     | -40  | _    | +85  | °C    |

Precautions: Although the MB15A01 contains an antistatic element to prevent electrostatic breakdown and the circuitry has been improved in electrostatic protection, observe the following precautions when handling the device:

- When storing or carrying the device, put it in a conductive case.

- This is static-sensitive device; take proper anti-ESD Paricutin. Ensure that personnel and equipment are properly grounded. Cover workbenches with grounded conductive mats.

- Before fitting the device into or removing it from the socket, turn the power supply off.

- Protect leads with conductive sheet when handling or transporting PC boards with devices.

### **■ ELECTRICAL CHARACTERISTICS**

$(Vcc = 2.7 V to 3.5 V, Ta = -40^{\circ}C to +85^{\circ}C)$

| <b>D</b>                            |              | 01               |                                                                                    | cc = 2.7  V t | Value | 10 0 10   |                  |

|-------------------------------------|--------------|------------------|------------------------------------------------------------------------------------|---------------|-------|-----------|------------------|

| Parameter                           |              | Symbol           | Condition                                                                          | Min.          | Тур.  | Max.      | Unit             |

| Power supply current                | t            | Icc              | Vcc = 3 V, assuming fin = 1.1<br>GHz and OSC <sub>IN</sub> = 12 MHz, in<br>locking | _             | 6.5   | _         | mA               |

| Operating frequency                 | fin          | fin              | Must be AC-coupled. The minimum operating frequency assumes coupling at 1000 pF.   | 10            | _     | 1100      | MHz              |

|                                     | OSCIN        | fosc             | _                                                                                  | _             | 12    | 23        | MHz              |

| Input sensitivity                   | fin          | V <sub>fin</sub> | 50 $\Omega$ system (Refer to the test circuit example)                             | -10           | _     | 6         | dBm              |

|                                     | OSCIN        | Vosc             | _                                                                                  | 0.5           | _     | _         | V <sub>P-P</sub> |

| "H" level input volt-<br>age        | Clock        | VIH              | _                                                                                  | Vcc × 0.7     | _     | _         | V                |

| "L" level input volt-<br>age        | - Data<br>LE | VIL              | _                                                                                  | _             | _     | Vcc × 0.3 | V                |

| "H" level input cur-<br>rent        | Clock        | Іін              | _                                                                                  | _             | _     | 1.0       | μΑ               |

| "L" level input cur-<br>rent        | Data         |                  | _                                                                                  | _             | _     | -1.0      | μΑ               |

| Input ourrent                       | OSCIN        | losc             | _                                                                                  | _             | ±50   | _         | μΑ               |

| Input current                       | LE, FC       | ILE              | _                                                                                  | _             | -60   | _         | μΑ               |

| "H" level output volt-<br>age       | øR, LD       | Vон              | Vcc = 3 V, Iон = -1.0 mA                                                           | 2.1           | _     | _         | V                |

| "L" level output volt-<br>age       | øP/R,<br>LD  | Vol              | Vcc = 3 V, IoL = 1.0 mA                                                            | _             | _     | 0.4       | V                |

| High-impedance Do cutoff current ØP |              | loff             | V <sub>P</sub> = V <sub>CC</sub> to 6.0 V<br>V <sub>OOP</sub> = GND to 6.0 V       | _             | _     | 1.1       | μΑ               |

|                                     | øR, LD       | Іон              | Vcc = 3 V                                                                          | -1.0          | _     | _         | mA               |

| Output current                      | øP/R,<br>LD  | Іоь              | Vcc = 3 V                                                                          |               |       | 1.0       | mA               |

### **■ FUNCTIONAL DESCRIPTIONS**

#### 1. Pulse Swallow Function

For the pulse swallow function, use the following equations to select their respective setting values:

$$f_{VCO} = ((P \times N) + A) \times f_{OSC} \div R$$

fvco : Output frequency of externally connected VCO

P : Prescaler divide ratio (64 or 128)

N : Divide ratio of 11-bit programmable counter (16 to 2047) A : Divide ratio of 7-bit swallow counter (0 to 127, A < N)

fosc : Reference oscillation frequency

R : Divide ratio of 14-bit programmable reference counter (6 to 16383)

#### 2. Serial Data Input Method

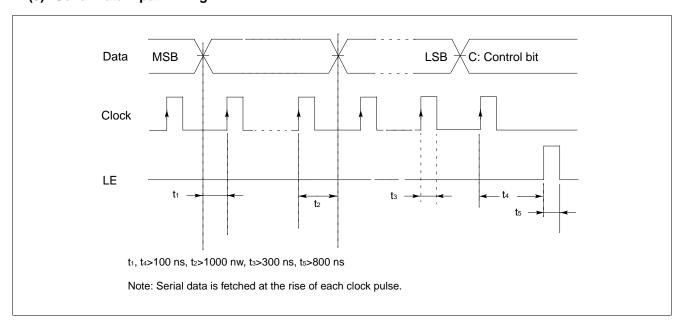

Serial data is processed using three input pins (Data, Clock, and LE pins) to control the 15-bit reference divider and the 18-bit programmable divider separately.

Input binary-coded serial data to the Data pin.

Serial data is input to the internal shift register in sequence at the rise of each clock pulse. When the load enable signal input pin has a high level (or open), the input data is transferred to the latch depending on the control bit.

Control bit = "H": Transfer to the 15-bit latch Control bit = "L": Transfer to the 18-bit latch

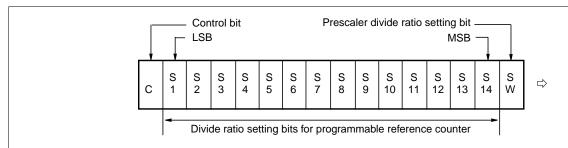

### (1) Divide Ratio of Reference Divider

The reference divider consists of a 16-bit shift register, a 15-bit latch, and a 14-bit reference counter. Serial data is made up of the following 16 bits:

#### • 14-bit programmable reference divide ratio

| Divide ratio | S<br>14 | S<br>13 | S<br>12 | S<br>11 | S<br>10 | S<br>9 | S<br>8 | S<br>7 | S<br>6 | S<br>5 | S<br>4 | S<br>3 | S<br>2 | S<br>1 |

|--------------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 6            | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 0      |

| 7            | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      |

| •            | •       | •       | •       | •       | •       | •      | •      | •      | •      | •      | •      | •      | •      | •      |

Note: The divide ratio must not be less than 6. (Set value: 6 to 16383)

SW: Prescaler division bit

SW = "H": 64/65 division SW = "L": 128/129 division

S1 to S14: Divide ratio setting bits (Divide ratio of 6 to 16383)

C: Control bit (Set it to "H".)

Note: Start data input with MSB first.

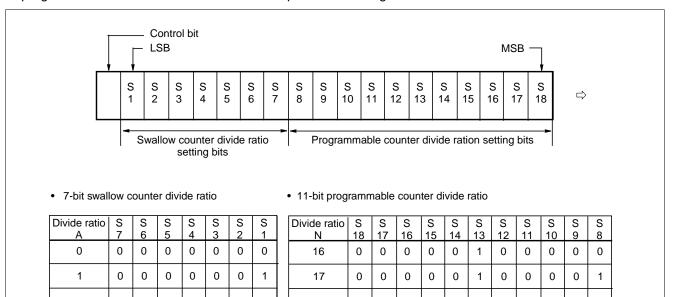

### (2) Divide Ratio of Programmable Divider

The programmable divider consists of a 19-bit shift register, an 18-bit latch, 7-bit swallow counter, and an 11-bit programmable counter. Serial data is made up of the following 19 bits:

(Set value: 0 to 127) Note: The divide ratio must not be less than 16. (Set value: 16 to 2047)

S1 to S7: Swallow counter divide ratio setting bits (Divide ration of 0 to 127)

S8 to S18: Programmable counter divide ration setting bits (Divide ration of 16 to 2047)

C: Control bit (Set it to "L")

Note: Start data input with MSB first.

### (3) Serial Data Input Timing

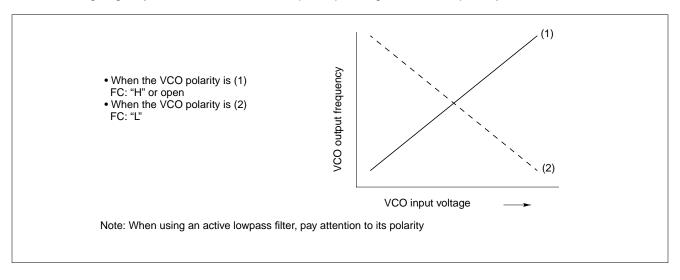

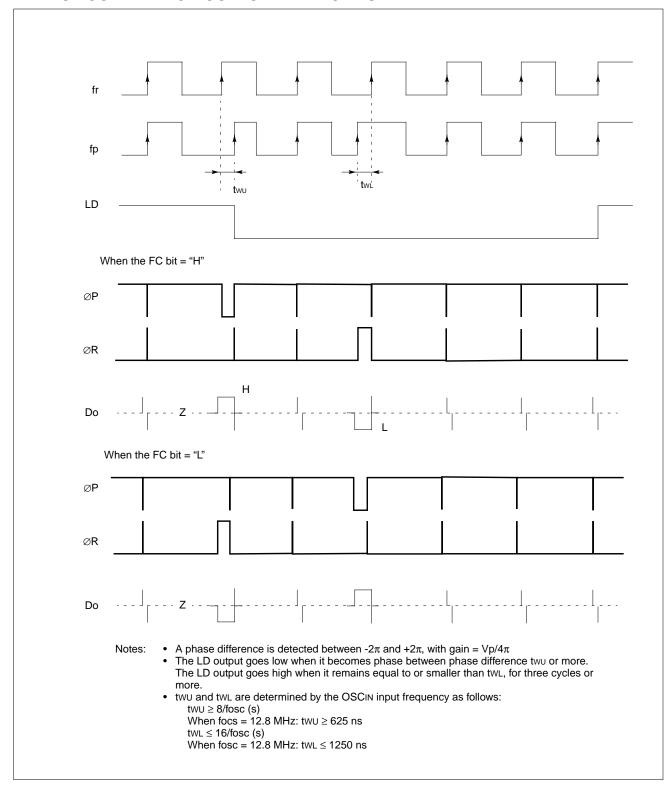

### 3. Relation between FC Pin Inputs and Phase Characteristics

The FC pin is the phase switching pin for the phase comparator. Controlling the FC pin inverts the characteristics of the internal charge pump output ( $D_0$ ) and phase comparator outputs ( $\emptyset R$ ,  $\emptyset P$ ). In addition, the phase comparator input monitor pin (fout) is also controlled via the FC pin. The following table lists relation between FC pin inputs and  $D_0$ ,  $\emptyset R$ ,  $\emptyset P$ , and fout:

|         |    | FC: "H" ( | (or open) |      | FC: "L" |    |    |      |

|---------|----|-----------|-----------|------|---------|----|----|------|

|         | Do | øR        | øΡ        | fout | Do      | øR | øΡ | fout |

| fr > fp | Н  | L         | L         |      | L       | Н  | Z  |      |

| fr < fp | L  | Н         | Z         | fr   | Н       | L  | L  | fp   |

| fr = fp | Z  | L         | Z         |      | Z       | L  | Z  |      |

### Z: High impedance

When designing a synthesizer, control the FC pin depending on the VCO polarity.

### **■ PHASE COMPARATOR OUTPUT WAVEFORMS**

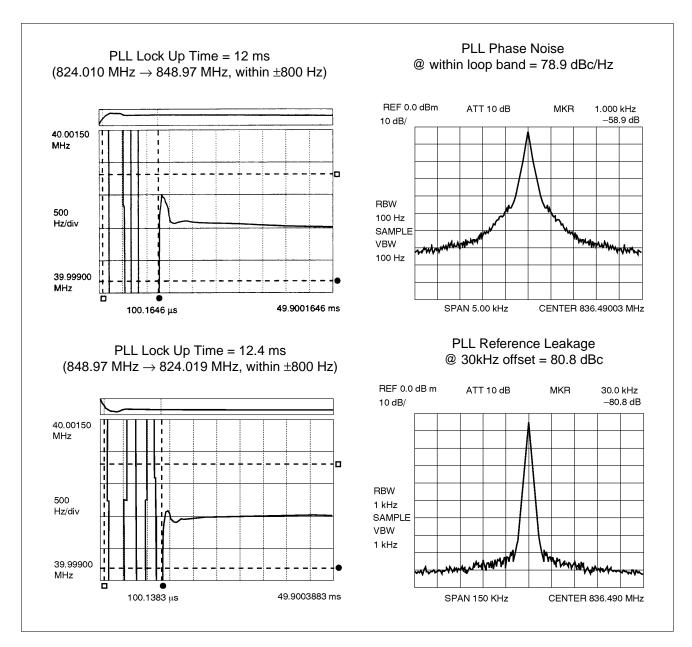

### **■ TYPICAL CHARACTERISTIC CURVES**

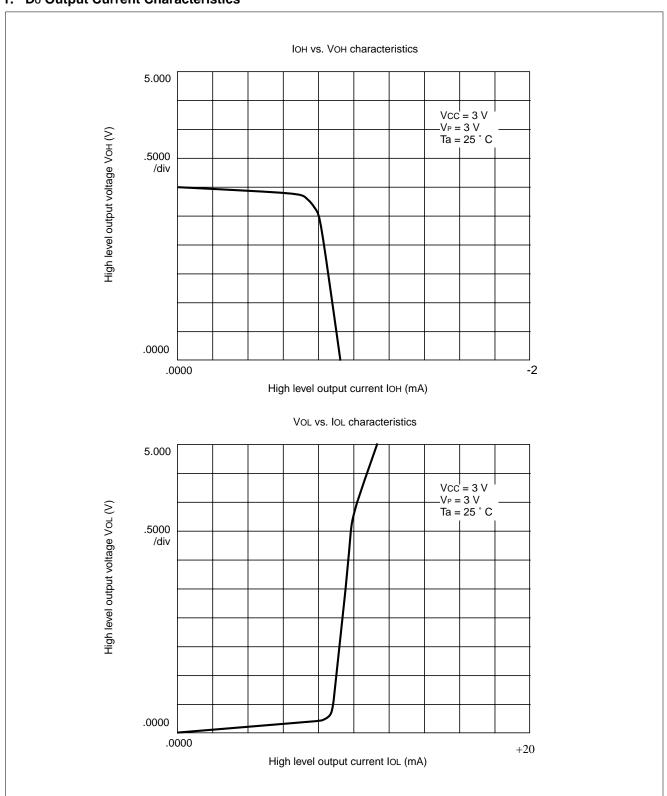

### 1. Do Output Current Characteristics

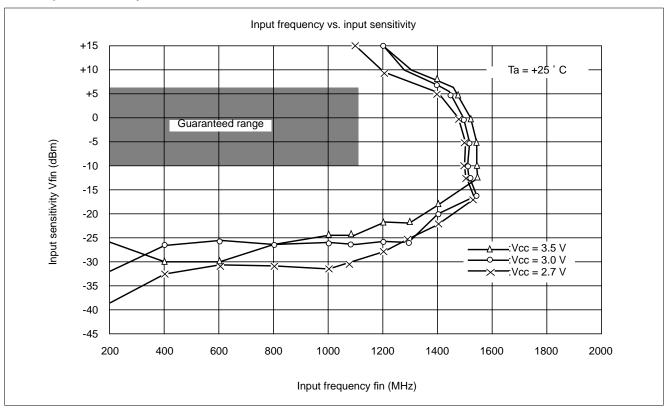

### 2. fin Input Sensitivity Characteristics

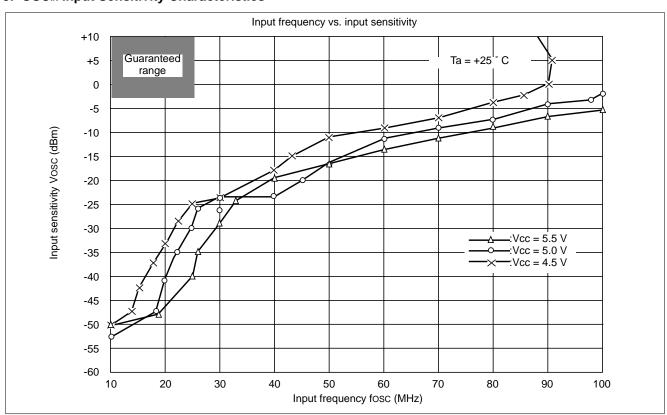

### 3. OSCIN Input Sensitivity Characteristics

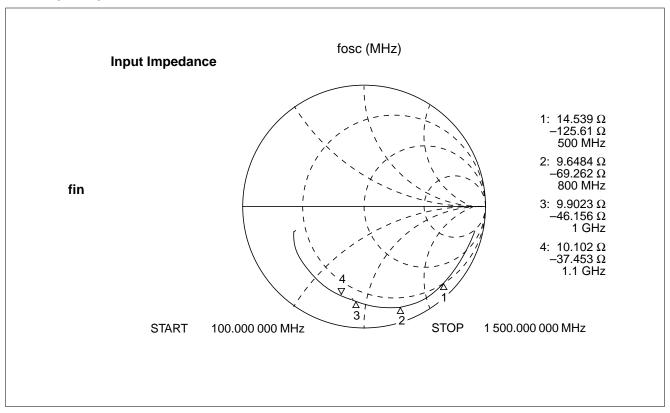

### 4. fin Input Impedance Characteristics

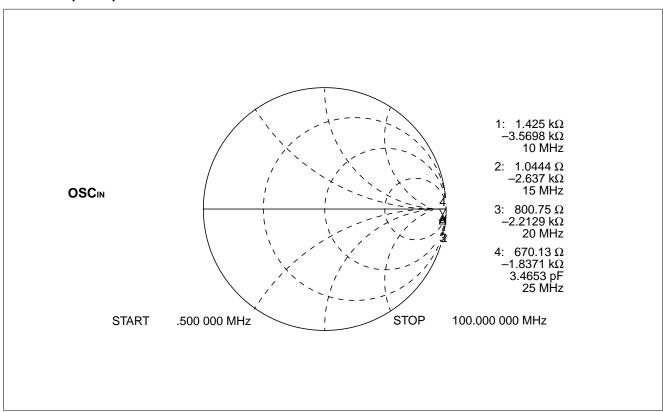

### 5. OSC<sub>IN</sub> Input Impedance Characteristics

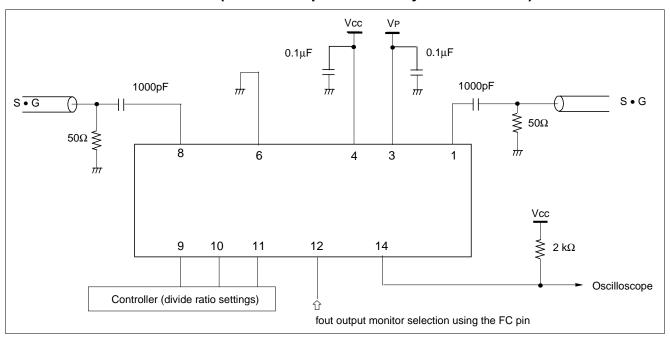

### ■ TEST CIRCUIT EXAMPLE (fin/OSC<sub>IN</sub> Input Sensitivity Measurement)

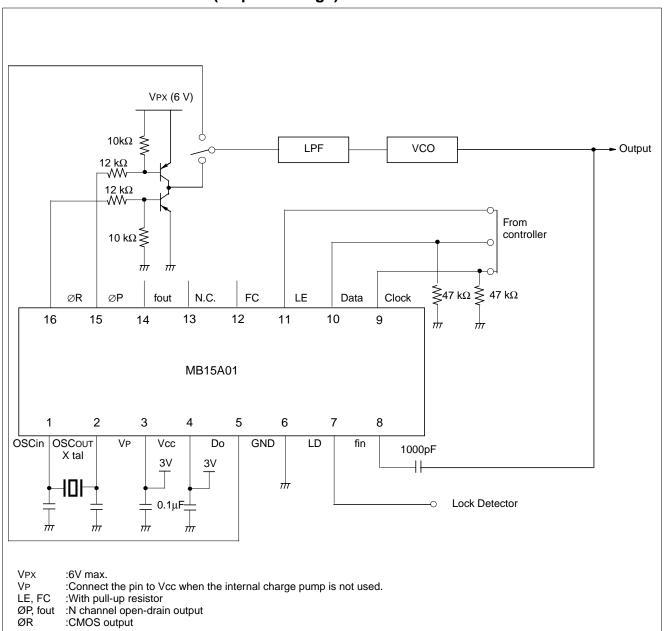

### ■ APPLICATION EXAMPLE (16-pin Package)

ØŔ

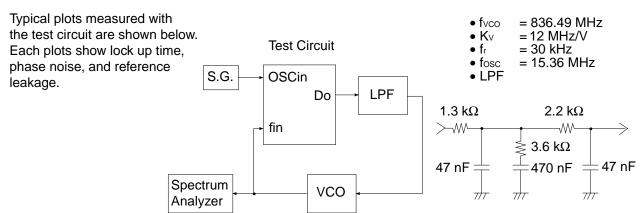

### **■ REFERENCE INFORMATION**

### ■ ORDERING INFORMATION

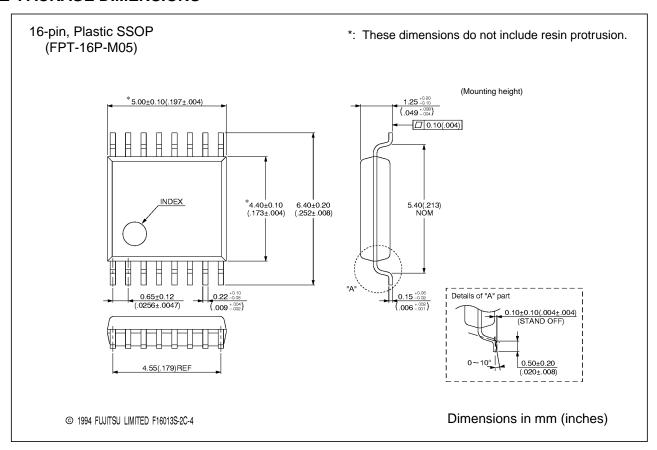

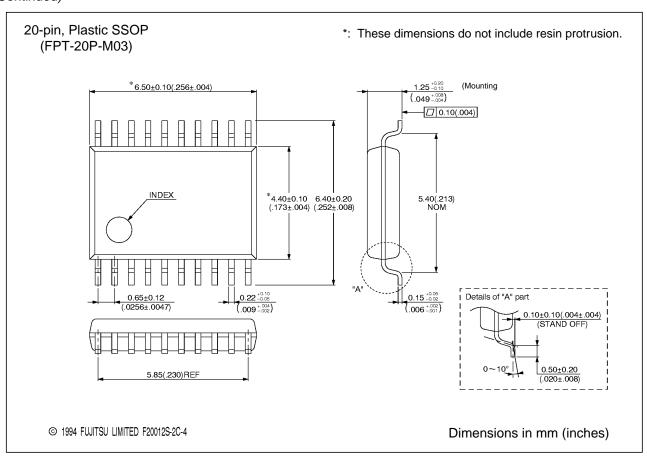

| Part number | Package                               | Remarks |

|-------------|---------------------------------------|---------|

| MB15A01PFV1 | 16-pin, Plastic SSOP<br>(FPT-16P-M05) |         |

| MB15A01PFV2 | 20-pin, Plastic SSOP<br>(FPT-20P-M03) |         |

### **■ PACKAGE DIMENSIONS**

(Continued)

(Continued)

## **Worldwide Headquarters**

Japan **Fujitsu Limited**

Tel: +81 44 754 3753 1015 Kamiodanaka Fax: +81 44 754 3332 Nakaharaku Kawasaki 211

Japan

http://www.fujitsu.co.jp/

USA

Tel: +1 408 922 9000 Fujitsu Microelectronics Inc Fax: +1 408 922 9179 3545 North First Street

San José CA 95134-1804

USA

Tel: +1 800 866 8608 Customer Response Center Fax: +1 408 922 9179 Mon-Fri: 7am-5pm (PST)

http://www.fujitsumicro.com/

Asia

+65 281 0770 Tel:

+65 281 0220

http://www.fsl.com.sg/

**Europe**

Tel: +49 6103 6900 Fax:

+49 6103 6901

Fujitsu Mikroelektronik **GmbH**

**Fujitsu Microelectronics Asia PTE Limited**

#05-08, 151 Lorong Chuan

New Tech Park

Singapore 556741

Am Siebenstein 6-10 D-63303 Dreieich-Buchschlag

Germany

http://www.fujitsu.ede.com/

All Right Reserved.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu Microelectronics, Inc. assumes no responsibility for inaccuracies.

The information conveyed in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu Limited, its subsidiaries, or Fujitsu Microelectronics, Inc.

Fujitsu Microelectronics, Inc. reserves the right to change products or specifications without notice.

No part of the publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu Microelectronics, Inc.

FJ No. DS04-21324-3E