# MPEG Clock Generator with VCXO

### **Features**

- Integrated phase-locked loop (PLL)

- Low-jitter, high-accuracy outputs

- VCXO with analog adjust

- 3.3V operation

- Compatible with MK3727 (-1, -5)

#### **Benefits**

- Highest-performance PLL tailored for multimedia applications

- Meets critical timing requirements in complex system designs

- Large ±150-ppm range, better linearity

- Application compatibility for a wide variety of designs

- Enables design compatibility

- Advanced Features

- Matches nonlinear MK3727A VCXO control curve (-5)

- Digital VCXO control

- Electromagnetic interference (EMI) reduction for standards compliance

- Second source for existing designs

| Part<br>Number | Outputs | Input Frequency Range                                     | Output<br>Frequencies | VCXO Control<br>Curve | Other Features                               |

|----------------|---------|-----------------------------------------------------------|-----------------------|-----------------------|----------------------------------------------|

| CY2410-1       | 1       | 13.5-MHz pullable crystal input per Cypress specification | 1 copy of 27 MHz      | linear                | Compatible with MK3727                       |

| CY2410-5       | 1       | 13.5-MHz pullable crystal input per Cypress specification | 1 copy of 27 MHz      |                       | Matches MK3727A nonlinear VCXO Control Curve |

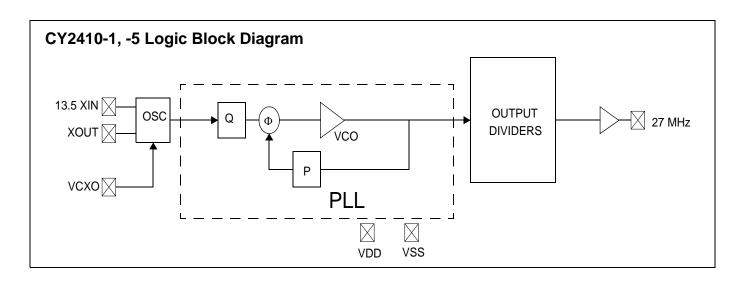

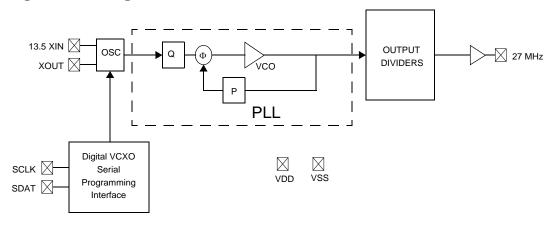

## CY2410-3 Logic Block Diagram

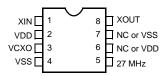

# **Pin Configuration**

Figure 1. CY2410-1, CY2401-5 8-Pin SOIC

Table 1. Pin Definitions for CY2410-1, -5

| Name                            | Pin Number | Description                               |

|---------------------------------|------------|-------------------------------------------|

| X <sub>IN</sub>                 | 1          | Reference crystal input                   |

| $V_{DD}$                        | 2          | Voltage supply                            |

| V <sub>CXO</sub>                | 3          | Input analog control for V <sub>CXO</sub> |

| V <sub>SS</sub>                 | 4          | Ground                                    |

| 27 MHz                          | 5          | 27-MHz clock output                       |

| NC/V <sub>DD</sub>              | 6          | No Connect or voltage supply              |

| NC/V <sub>SS</sub>              | 7          | No Connect or ground                      |

| X <sub>OUT</sub> <sup>[1]</sup> | 8          | Reference crystal output                  |

#### Note

<sup>1.</sup> Float  $X_{\mbox{\scriptsize OUT}}$  if  $X_{\mbox{\scriptsize IN}}$  is externally driven.

# Pullable Crystal Specifications [2]

| Parameter                      | Description                                              | Condition                                                                             | Min  | Тур. | Max  | Unit |

|--------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|------|

| F <sub>NOM</sub>               | Nominal crystal frequency                                | Parallel resonance, funda-<br>mental mode, AT cut                                     | _    | 13.5 | _    | MHz  |

| C <sub>LNOM</sub>              | Nominal load capacitance                                 |                                                                                       | -    | 14   | _    | pF   |

| R <sub>1</sub>                 | Equivalent series resistance (ESR)                       | Fundamental mode                                                                      | -    | _    | 25   | Ω    |

| R <sub>3</sub> /R <sub>1</sub> | Ratio of third overtone mode ESR to fundamental mode ESR | Ratio used because typical R <sub>1</sub> values are much less than the maximum spec. | 3    | _    | _    |      |

| DL                             | Crystal drive level                                      | No external series resistor assumed                                                   | _    | 0.5  | 2.0  | mW   |

| F <sub>3SEPHI</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | High side                                                                             | 300  | _    | _    | ppm  |

| F <sub>3SEPLO</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | Low side                                                                              | -    | _    | -150 | ppm  |

| C <sub>0</sub>                 | Crystal shunt capacitance                                |                                                                                       | _    | _    | 7    | pF   |

| C <sub>0</sub> /C <sub>1</sub> | Ratio of shunt to motional capacitance                   |                                                                                       | 180  | _    | 250  |      |

| C <sub>1</sub>                 | Crystal motional capacitance                             |                                                                                       | 14.4 | 18   | 21.6 | pF   |

Note

2. Crystals that meet this specification includes: Ecliptek ECX-5788-13.500M, Siward XTL001050A-13.5-14-400, Raltron A-13.500-14-CL, PDI HA13500XFSA14XC.

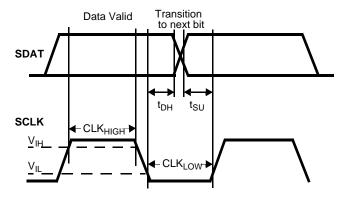

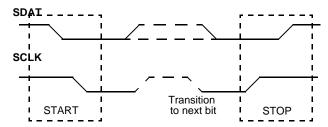

Figure 2. Data Valid and Data Transition Periods

Figure 3. Start and Stop Frame

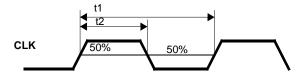

Figure 4. Duty Cycle Definition; DC = t2/t1

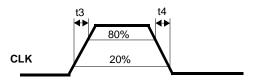

Figure 5. Rise and Fall Time Definitions: ER =  $0.6 \times VDD / t3$ , EF =  $0.6 \times VDD / t4$

## **Absolute Maximum Conditions**

| Parameter      | Description                                 | Min                   | Max                   | Unit |

|----------------|---------------------------------------------|-----------------------|-----------------------|------|

| $V_{DD}$       | Supply Voltage                              | -0.5                  | 7.0                   | V    |

| T <sub>S</sub> | Storage Temperature <sup>[3]</sup>          | -65                   | 125                   | °C   |

| T <sub>J</sub> | Junction Temperature                        | _                     | 125                   | °C   |

|                | Digital Inputs                              | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V    |

|                | Digital Outputs referred to V <sub>DD</sub> | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V    |

|                | Electrostatic Discharge                     | 2000                  |                       | V    |

# **Recommended Operating Conditions**

| Parameter         | Description                                                                                         | Min   | Тур. | Max   | Unit |

|-------------------|-----------------------------------------------------------------------------------------------------|-------|------|-------|------|

| $V_{DD}$          | Operating Voltage                                                                                   | 3.135 | 3.3  | 3.465 | V    |

| T <sub>A</sub>    | Ambient Temperature                                                                                 | 0     | _    | 70    | °C   |

| C <sub>LOAD</sub> | Max. Load Capacitance                                                                               | 1     | _    | 15    | pF   |

| f <sub>REF</sub>  | Reference Frequency                                                                                 | 1     | 13.5 | -     | MHz  |

| t <sub>PU</sub>   | Power up time for V <sub>DD</sub> to reach minimum specified voltage (power ramp must be monotonic) | 0.05  | _    | 500   | ms   |

## **DC Electrical Specifications**

| Parameter         | Name                                     | Description                            | Min          | Тур. | Max      | Unit |

|-------------------|------------------------------------------|----------------------------------------|--------------|------|----------|------|

| I <sub>OH</sub>   | Output HIGH Current –1,–5                | $V_{OH} = V_{DD} - 0.5, V_{DD} = 3.3V$ | 12           | 24   | _        | mA   |

| I <sub>OL</sub>   | Output LOW Current -1,-5                 | $V_{OL} = 0.5, V_{DD} = 3.3V$          | 12           | 24   | _        | mA   |

| C <sub>IN</sub>   | Input Capacitance                        |                                        | _            | _    | 7        | pF   |

| I <sub>IZ</sub>   | Input Leakage Current                    |                                        | _            | 5    | _        | μΑ   |

| $f_{\Delta XO}$   | V <sub>CXO</sub> pullability range:-1,-5 |                                        | <u>+</u> 150 | _    | _        | ppm  |

| V <sub>VCXO</sub> | V <sub>CXO</sub> input range             |                                        | 0            | _    | $V_{DD}$ | V    |

| $I_{VDD}$         | Supply Current                           |                                        | _            | 30   | 35       | mA   |

# AC Electrical Specifications $(V_{DD} = 3.3V)^{[4]}$

| Parameter <sup>[4]</sup> | Name                     | Description                                                                                       | Min | Тур. | Max | Unit |

|--------------------------|--------------------------|---------------------------------------------------------------------------------------------------|-----|------|-----|------|

| DC                       | Output Duty Cycle        | Duty Cycle is defined in Figure 4, 50% of V <sub>DD</sub>                                         | 45  | 50   | 55  | %    |

| ER <sub>OR</sub>         | Rising Edge Rate –1, –5  | Output Clock Edge Rate, Measured from 20% to 80% of V <sub>DD</sub> , CLOAD = 15 pF See Figure 5. | 0.8 | 1.4  | _   | V/ns |

| ER <sub>OF</sub>         | Falling Edge Rate –1, –5 | Output Clock Edge Rate, Measured from 80% to 20% of V <sub>DD</sub> , CLOAD = 15 pF See Figure 5. | 8.0 | 1.4  | _   | V/ns |

| t <sub>9</sub>           | Clock Jitter –1, –5      | Peak-to-peak period jitter                                                                        | _   | 140  | _   | ps   |

| t <sub>10</sub>          | PLL Lock Time            |                                                                                                   | _   | _    | 3   | ms   |

- Rated for ten years.

Not 100% tested.

Figure 6. Test and Measurement Setup

## **Ordering Information**

| Ordering Code               | Package Type               | Operating<br>Range | Operating Voltage | Features                                     |

|-----------------------------|----------------------------|--------------------|-------------------|----------------------------------------------|

| Pb-Free                     |                            |                    |                   |                                              |

| CY2410SXC-1 <sup>[5]</sup>  | 8-pin SOIC                 | Commercial         | 3.3V              | Linear VCXO control curve                    |

| CY2410SXC-1T <sup>[5]</sup> | 8-pin SOIC - Tape and Reel | Commercial         | 3.3V              | Linear VCXO control curve                    |

| CY2410SXC-5 <sup>[5]</sup>  | 8-pin SOIC                 | Commercial         | 3.3V              | Matches nonlinear MK3727A VCXO control curve |

| CY2410SXC-5T <sup>[5]</sup> | 8-pin SOIC - Tape and Reel | Commercial         | 3.3V              | Matches nonlinear MK3727A VCXO control curve |

| CY2410KSXC-5                | 8-pin SOIC                 | Commercial         | 3.3V              | Matches nonlinear MK3727A VCXO control curve |

| CY2410KSXC-5T               | 8-pin SOIC - Tape and Reel | Commercial         | 3.3V              | Matches nonlinear MK3727A VCXO control curve |

# **Package Drawing and Dimensions**

Figure 7. 8-Lead (150-Mil) SOIC 1. DIMENSIONS IN INCHES[MM] MIN. MAX. 2. PIN 1 ID IS OPTIONAL, ROUND ON SINGLE LEADFRAME 0.150[3.810] RECTANGULAR ON MATRIX LEADFRAME 0.157[3.987] 3. REFERENCE JEDEC MS-012 0.230[5.842] 4. PACKAGE WEIGHT 0.07gms 0.244[6.197] PART# S08.15 STANDARD PKG. SZ08.15 LEAD FREE PKG. 0.189[4.800] 0.010[0.254] X 45° SEATING PLANE 0.196[4.978] 0.016[0.406] 0.061[1.549] 0.068[1.727] 0.004[0.102] 0.050[1.270] BSC 0.0075[0.190] 0.004[0.102] 0°~8° 0.016[0.406] 0.0098[0.249] 0.0098[0.249] 0.035[0.889] 0.0138[0.350] 51-85066 \*C 0.0192[0.487]

#### Note

<sup>5.</sup> Not recommended for new designs.

### **Document History Page**

|      | Title: CY2410<br>Number: 38- | 0 MPEG Clock<br>07317 | Generator v        | vith VCXO                                                                                                                                                                                                                                                                                                                                               |

|------|------------------------------|-----------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV. | ECN NO.                      | Submission<br>Date    | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                   |

| **   | 111553                       | 02/12/02              | CKN                | New Data Sheet                                                                                                                                                                                                                                                                                                                                          |

| *A   | 114937                       | 09/24/02              | CKN                | Added -6 to data sheet, Advance Information to Final                                                                                                                                                                                                                                                                                                    |

| *B   | 121418                       | 12/06/02              | CKN                | Updated the Pullable Crystal Specifications table on page 2                                                                                                                                                                                                                                                                                             |

| *C   | 126905                       | 06/17/03              | RGL                | Added -7 part to data sheet Added new parameter on the Pullable Crystal table Power up requirements added to the operating conditions                                                                                                                                                                                                                   |

| *D   | 131100                       | 01/20/03              | RGL                | Added VCXO –7 pullability range in the DC Specs with min. value of ±115ppm                                                                                                                                                                                                                                                                              |

| *E   | 2440886                      | See ECN               | AESA               | Updated template. Added Note "Not recommended for new designs." Added part number CY2410SXC-1, CY2410SXC-1T, CY2410SXC-5, CY2410SXC-5T, CY2410KSXC-5, and CY2410KSXC-5T in ordering information table. Removed all part numbers for non-Pb-free packages (part numbers beginning CY2410SC). Removed details specific to the -3, -4, -6 and -7 versions. |

## Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

| Products         |                      | PSoC Solutions        |                                   |

|------------------|----------------------|-----------------------|-----------------------------------|

| PSoC             | psoc.cypress.com     | General               | psoc.cypress.com/solutions        |

| Clocks & Buffers | clocks.cypress.com   | Low Power/Low Voltage | psoc.cypress.com/low-power        |

| Wireless         | wireless.cypress.com | Precision Analog      | psoc.cypress.com/precision-analog |

| Memories         | memory.cypress.com   | LCD Drive             | psoc.cypress.com/lcd-drive        |

| Image Sensors    | image.cypress.com    | CAN 2.0b              | psoc.cypress.com/can              |

|                  |                      | USB                   | psoc.cypress.com/usb              |

© Cypress Semiconductor Corporation, 2002-2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 38-07317 Rev. \*E

Revised May 22, 2008

Page 8 of 8

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Cypress Semiconductor:

CY2410SXC-1 CY2410SXC-1T CY2410SXC-5 CY2410SXC-5T