# **Dual Output Low Noise LDO Linear Regulator**

#### POWER MANAGEMENT

#### **Features**

- Input voltage range 2.5 to 5.5V

- Output voltages 2.8V and 1.8V (SC1458A), 2.85V and 2.85V (SC1458B)

- Maximum output current 300mA (each LDO)

- Low 200mV maximum dropout at 200mA load

- Quiescent current 100µA (both LDOs enabled)

- Shutdown current 100nA

- Output noise < 50µV<sub>RMS</sub> (SC1458B)

- PSRR > 65dB at 1kHz (SC1458B)

- Space saving package MLPD-W6, 3mm x 3mm

- Over-temperature protection

- Short-circuit protection

- Under-voltage lockout

- Reset monitor for output A (SC1458A)

## **Applications**

- PDAs and cellular phones

- GPS devices

- Palmtop computers and handheld instruments

- TFT/LCD applications

- Wireless handsets

- Digital cordless phones and PCS phones

- Personal communicators

- Two-way pagers

- Wireless LAN

## **Description**

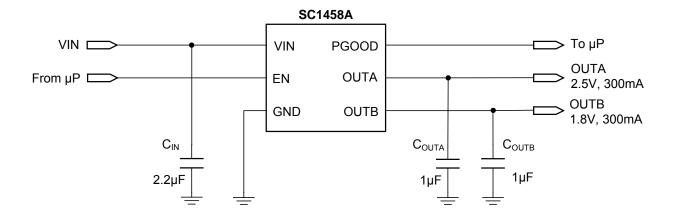

The SC1458 is a family of dual output, ultra-low dropout linear voltage regulators designed for use in battery powered wireless applications. Both versions of the SC1458 require an input voltage level between 2.5V and 5.5V. The SC1458A supplies 2.5V on OUTA and 1.8V on OUTB, while SC1458B supplies 2.85V on both outputs. (For other voltage options see the SC560).

The SC1458A provides a PGOOD output to hold a processor in reset when the voltage on OUTA is not in regulation. The SC1458B provides superior low-noise performance by using an external bypass capacitor to filter the bandgap reference. Both versions have a single enable pin that controls both LDO outputs. The startup sequence delays the start of OUTB by 128µs after OUTA is enabled.

Each version also provides protection circuitry such as current limiting, under-voltage lockout, and thermal protection to prevent device failures. Stability is maintained by using  $1\mu F$  capacitors on the output pins. The MLPD package and 0402 ceramic capacitors minimize the required PCB area.

# **Typical Application Circuit**

September 12, 2007 1

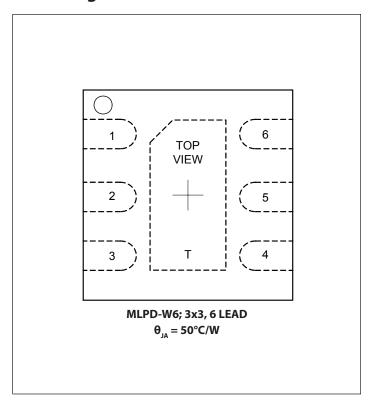

# **Pin Configuration**

# **Ordering Information**

| Device                         | Package          |

|--------------------------------|------------------|

| SC1458AWLTRT <sup>(1)(2)</sup> | MLPD-W6 3x3      |

| SC1458BWLTRT <sup>(1)(2)</sup> | MLPD-W6 3x3      |

| SC1458AEVB                     | Evaluation Board |

| SC1458BEVB                     | Evaluation Board |

#### Notes

- (1) Available in tape and reel only. A reel contains 3,000 devices.

- (2) Available in lead-free package only. Device is WEEE and RoHS compliant.

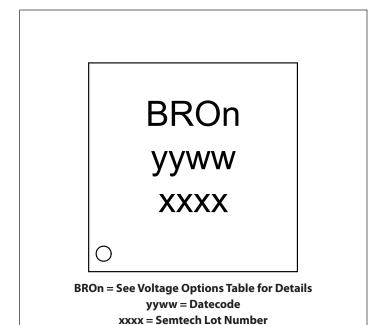

# **Marking Information**

# **Voltage Options**

| Device  | Marking ID | <b>V</b> <sub>LDOA</sub> | <b>V</b> <sub>LDOB</sub> |

|---------|------------|--------------------------|--------------------------|

| SC1458A | BROA       | 2.5V                     | 1.8V                     |

| SC1458B | BROB       | 2.85V                    | 2.85V                    |

# **Absolute Maximum Ratings**

| $V_{IN}(V)$ 0.3 to +6.5                                 |

|---------------------------------------------------------|

| $V_{EN}(V)$ -0.3 to $(V_{IN} + 0.3)$                    |

| $V_{PGOOD}(V)$ 0.3 to $(V_{IN} + 0.3)$                  |

| Pin Voltage — All Other Pins (V)0.3 to $(V_{IN} + 0.3)$ |

| $V_{OUTA'}, V_{OUTB'}$ Short Circuit DurationContinuous |

| ESD Protection Level <sup>(1)</sup> (kV)                |

# **Recommended Operating Conditions**

| Ambient Temperature Range (°C) | $-40 \le T_{_A} \le +85$ |

|--------------------------------|--------------------------|

| VIN (V)                        | $2.5 \le V_{IN} \le 5.5$ |

## **Thermal Information**

| Thermal Resistance, Junction to Ambient $^{(2)}$ (°C/W) 50       |

|------------------------------------------------------------------|

| $Maximum\ Junction\ Temperature\ (^{\circ}C)\ \dots \dots + 150$ |

| Storage Temperature Range (°C)65 to +150                         |

| Peak IR Reflow Temperature (10s to 30s) (°C) $\dots +260$        |

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### NOTES:

- (1) Tested according to JEDEC standard JESD22-A114-B.

- (2) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

### Electrical Characteristics \_\_\_\_\_

Unless otherwise noted  $V_{IN}=3.6V$ ,  $C_{IN}=2.2\mu F$ ,  $C_{OUTA}=C_{OUTB}=1\mu F$ ,  $V_{EN}=V_{IN}$ ,  $T_A=-40$  to  $+85^{\circ}C$ . Typical values are at  $T_A=25^{\circ}C$ . All specifications apply to both LDOs unless otherwise noted.

| Parameter                      | Symbol                 | Conditions                                                                                                  | Min | Тур | Max | Units            |

|--------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|------------------|

| Input Supply Voltage Range     | V <sub>IN</sub>        |                                                                                                             | 2.5 |     | 5.5 | V                |

| Output Voltage Accuracy        | $\Delta V_{_{ m OUT}}$ | $V_{IN} = V_{OUT} + 0.3V \text{ to } 5.5V, I_{OUT} = 0 \text{ to } 300\text{mA}$                            | -3  |     | 3   | %                |

| Maximum Output Current         | I <sub>MAX</sub>       |                                                                                                             | 300 |     |     | mA               |

| Dropout Voltage <sup>(1)</sup> | V <sub>D</sub>         | $I_{OUT} = 200 \text{mA}, V_{OUT} = 2.5 \text{V}$                                                           |     | 100 | 200 | mV               |

| Shutdown Current               | I <sub>SD</sub>        | T <sub>A</sub> = 25°C                                                                                       |     | 0.1 | 1   | μΑ               |

| Quiescent Current              | I <sub>Q</sub>         | $I_{OUTA} = I_{OUTB} = 0$ mA, $T_A = 25$ °C                                                                 |     | 100 |     | μΑ               |

| Load Regulation                | V <sub>LOAD</sub>      | $I_{OUT} = 1 \text{ mA to } I_{MAX}$                                                                        |     |     | 20  | mV               |

| Line Regulation                | V <sub>LINE</sub>      | I <sub>OUT</sub> = 1mA                                                                                      | -6  |     | 6   | mV               |

| Current Limit                  | I <sub>LIM</sub>       |                                                                                                             | 350 |     | 850 | mA               |

| Noise <sup>(2)</sup>           | e <sub>N</sub>         | $V_{IN} = 3.7V$ , $I_{OUT} = 50 \text{mA}$ , $10 \text{Hz} < f < 100 \text{kHz}$ , $C_{BYP} = 22 \text{nF}$ |     | 50  |     | $\mu V_{_{RMS}}$ |

|                                | IN IN                  | $V_{IN} = 3.7V$ , $I_{OUT} = 50 \text{mA}$ , $10 \text{Hz} < f < 100 \text{kHz}$                            |     | 300 |     | $\mu V_{_{RMS}}$ |

# **Electrical Characteristics (continued)**

| Parameter                                   | Symbol                                | Conditions                                                             | Min  | Тур  | Max  | Units |

|---------------------------------------------|---------------------------------------|------------------------------------------------------------------------|------|------|------|-------|

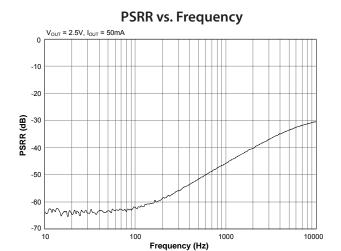

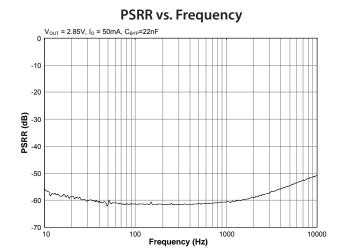

| Power Supply Rejection Ratio <sup>(2)</sup> | PSRR                                  | $V_{IN} = 3.7V$ , $I_{OUT} = 50$ mA, $f = 1$ kHz,<br>$C_{BYP} = 22$ nF |      | 65   |      | dB    |

| 11,7,7                                      |                                       | $V_{IN} = 3.7V$ , $I_{OUT} = 50$ mA, $f = 1$ kHz                       |      | 40   |      |       |

| PGOOD Delay <sup>(3)</sup>                  | t <sub>PGOOD</sub>                    |                                                                        | 160  | 200  | 240  | ms    |

| PGOOD Threshold <sup>(3)</sup>              | V <sub>TH(PGOOD)</sub>                | $V_{\text{OUT(LDOA)}}$ falling                                         | 82   | 87   | 92   | %     |

| Start-Up Time                               | t <sub>su</sub>                       | From OFF to 87% $V_{OUT}$ , $I_{OUT} = 50$ mA, $C_{BYP} = 22$ nF       |      | 1    |      | ms    |

| Power Up Delay Between LDOA and LDOB        | t <sub>DELAY</sub>                    | Delay between 0.87V $_{\rm OUTA}$ and V $_{\rm OUTB}$ start-up         |      | 128  |      | μs    |

| Under Voltage Lockout                       | V <sub>UVLO</sub>                     | V <sub>IN</sub> Rising                                                 | 2.15 | 2.25 | 2.35 | V     |

| UVLO Hysteresis                             | V <sub>UVLO-HYS</sub>                 |                                                                        |      | 100  |      | mV    |

| Over Temperature Protection<br>Threshold    | T <sub>ot</sub>                       | Rising threshold                                                       |      | 160  |      | °C    |

| Over Temperature<br>Hysteresis              | T <sub>OT-HYS</sub>                   |                                                                        |      | 20   |      | °C    |

| Digital Inputs                              |                                       |                                                                        | '    |      |      |       |

| Logic Input High Threshold                  | V <sub>IH</sub>                       | V <sub>IN</sub> = 5.5V                                                 | 1.25 |      |      | V     |

| Logic Input Low Threshold                   | V <sub>IL</sub>                       | V <sub>IN</sub> = 2.5V                                                 |      |      | 0.4  | V     |

| Logic Input High Current                    | I <sub>IH</sub>                       | V <sub>IN</sub> = 5.5V                                                 |      |      | 1    | μΑ    |

| Logic Input Low Current                     | I <sub>IL</sub>                       | V <sub>IN</sub> = 5.5V                                                 |      |      | 1    | μΑ    |

| Digital Outputs                             | · · · · · · · · · · · · · · · · · · · |                                                                        |      |      |      | 1     |

| PGOOD Output Voltage Low                    | V <sub>OL</sub>                       | $I_{SINK} = 500 \mu A, V_{IN} = 3.7 V$                                 |      | 7    | 20   | mV    |

#### Notes:

- (1) Dropout voltage is defined as  $V_{IN} V_{OUT'}$  when  $V_{OUT}$  is 100 mV below the value of  $V_{OUT}$  for  $V_{IN} = V_{OUT} + 0.5$  V.

- (2) SC1458B only

- (3) SC1458A only

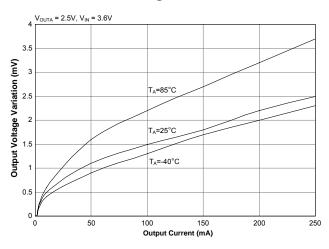

# **Typical Characteristics**

#### **Load Regulation LDOA**

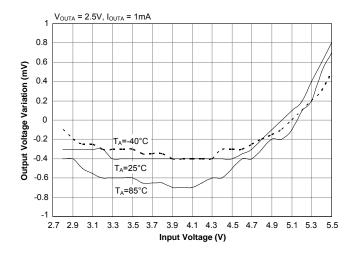

# Line Regulation LDOA

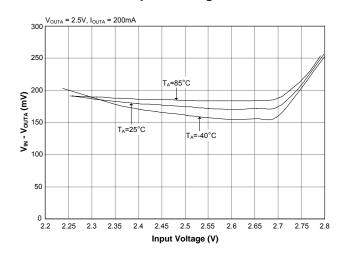

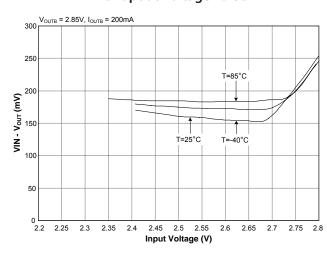

#### **Dropout Voltage LDOA**

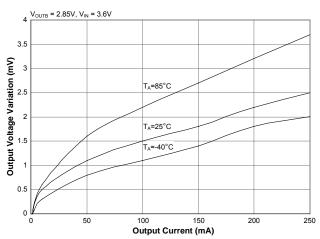

#### **Load Regulation LDOB**

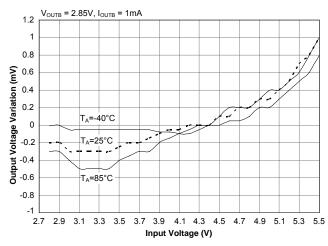

## **Line Regulation LDOB**

#### **Dropout Voltage LDOB**

# **Typical Characteristics (continued)**

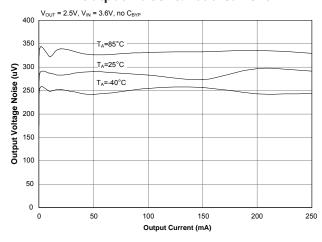

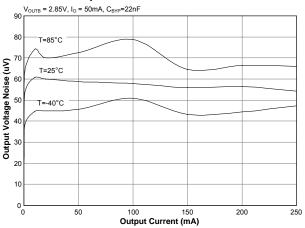

#### **Output Noise vs. Load Current**

#### **Output Noise vs. Load Current**

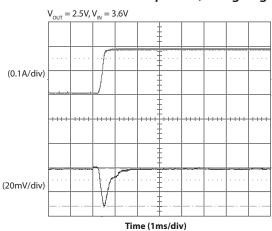

## Load Transient Response (Rising Edge)

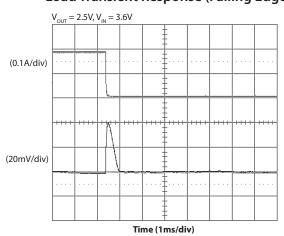

#### Load Transient Response (Falling Edge)

# **Pin Descriptions**

| Pir     | n #     | Din Nama       | Din Farantia a                                                                                                 |  |

|---------|---------|----------------|----------------------------------------------------------------------------------------------------------------|--|

| SC1458A | SC1458B | Pin Name       | Pin Function                                                                                                   |  |

| 1       | 1       | OUTB           | Output for LDOB                                                                                                |  |

| 2       | 2       | VIN            | Input supply voltage terminal                                                                                  |  |

| 3       | 3       | OUTA           | Output for LDOA                                                                                                |  |

| 4       | 4       | GND            | Analog and digital ground                                                                                      |  |

| 5       | 5       | EN             | Logic Input — active high enables the SC1458.                                                                  |  |

| 6       |         | PGOOD          | Open drain logic output — monitors output of LDOA, switches low when the output drops out of regulation.       |  |

|         | 6       | ВҮР            | LDO bypass output — bypass with a 22nF capacitor.                                                              |  |

| Т       | Т       | Thermal<br>Pad | Pad is for heatsinking purposes — not connected internally. Connect exposed pad to ground using multiple vias. |  |

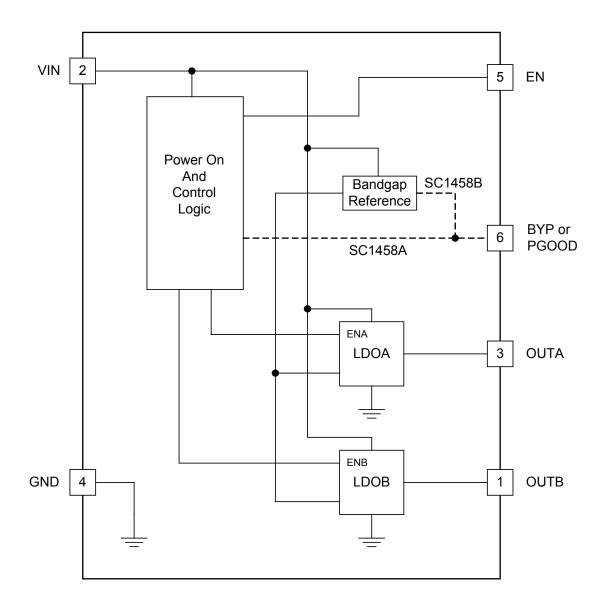

# **Block Diagram**

## **Applications Information**

#### **General Description**

The SC1458 is a dual output linear regulator intended for applications where low dropout voltage, low supply current, and low output noise are critical. The device provides a very simple, low cost solution for two separate regulated outputs using very little PCB area due to its small package size and the need for only three external capacitors.

Both linear regulators are powered from a single input voltage supply rail, and each provides 300mA of output current. Output voltages are set internally, eliminating the need for external resistors.

An active high enable pin (EN) controls operation of both regulators. Pulling this pin low causes the device to enter a very low power shutdown mode, where it typically draws 100nA from the input supply.

The device is available in two versions: SC1458A and SC1458B. The SC1458A version has pin 6 configured as a power good signal (PGOOD), which monitors the output of LDOA. The SC1458B device has pin 6 configured as an external bypass pin (BYP). This is suitable for applications which require low output noise and excellent PSRR characteristics.

#### **Power-On Control**

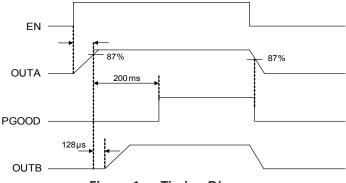

When EN transitions high, the output of LDOA is enabled. After a delay of 128µs, the output of LDOB is enabled. In the case of the SC1458A, when the output voltage of LDOA reaches 87% of its regulation point, the delay timer starts and the PGOOD signal transitions high after a delay of 200ms. The power up/down sequence is shown in Figure 1.

Figure 1 — Timing Diagram

#### **Active Shutdown**

The SC1458 has internal active shutdown circuitry included for both LDOs. Shutdown behavior is controlled by discharging the output capacitor on the LDO output by an on-chip FET when the LDO is disabled.

#### **Protection Circuitry**

The device provides the following protection features to ensure that no damage is incurred in the event of a fault condition.

- Under-Voltage Lockout

- Over-Temperature Protection

- Short-Circuit Protection

#### **Under-Voltage Lockout**

The Under-Voltage LockOut (UVLO) circuit protects the device from operating in an unknown state if the input voltage supply is too low.

When the  $V_{\rm IN}$  drops below the UVLO threshold, the LDOs are disabled and discharged — PGOOD is held low (SC1458A only). When  $V_{\rm IN}$  is increased above the hysteresis level, the LDOs are enabled into their previous states (timing described in Figure 1), provided EN has remained high. When powering-up with  $V_{\rm IN}$  below the UVLO threshold, the LDOs will remain off and PGOOD will be held low (SC1458A only).

#### **Over-Temperature Protection**

An internal over-temperature (OT) protection circuit is provided that monitors the internal junction temperature. When the temperature exceeds the OT threshold as defined in the Electrical Characteristics section, the OT protection disables all the LDO outputs and holds the PGOOD signal low. When the junction temperature drops below the hysteresis level, the LDOs are re-enabled into their previous states and PGOOD is set high, provided EN has remained high (SC1458A only).

#### **Short-Circuit Protection**

Each LDO output has short-circuit protection. If the output current exceeds the current limit, the output voltage will drop and the output current will be limited until the short is removed. If a short-circuit occurs on the output of LDOA, the output of LDOB will also be disabled

### **Applications Information (continued)**

until the fault is removed and the load current returns to a specified level.

#### **Component Selection**

A capacitance of 1µF or larger on each output is recommended to ensure stability. Ceramic capacitors of type X5R or X7R should be used because of their low ESR and stable temperature coefficients. It is also recommended that the input be bypassed with a 2.2µF, low ESR X5R or X7R capacitor to minimize noise and improve transient response. Note: Tantalum and Y5V capacitors are not recommended.

bypass capacitor (minimum of 22nF) should be connected between the BYP and GND pins to meet all noise-sensitive requirements. Increasing the capacitance to 100nF will further improve PSRR and output noise (SC1458B only).

#### **Thermal Considerations**

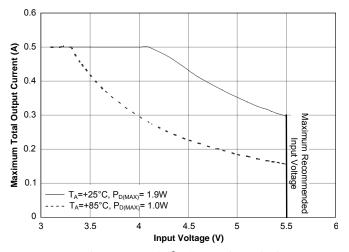

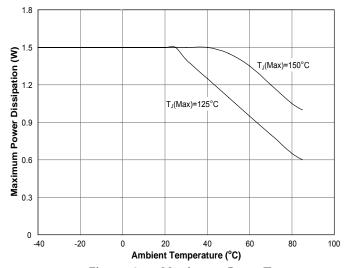

Although each of the two LDOs in the SC1458 can provide 300mA of output current, the maximum power dissipation in the device is restricted by the miniature package size. The graphs in Figure 2 and Figure 3 can be used as a guideline to determine whether the input voltage, output voltages, output currents, and ambient temperature of the system result in power dissipation within the operating limits or if further thermal relief is required.

Figure 2 — Safe Operating Limit

Figure 3 — Maximum P<sub>D</sub> vs. T<sub>A</sub>

The following procedure can be followed to determine if the thermal design of the system is adequate. The junction temperature of the SC1458 can be determined in known operating conditions using the following equation:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

where

$T_i = Junction Temperature (°C)$

$T_{\Delta} = Ambient Temperature (°C)$

$P_D = Power Dissipation (W)$

$\theta_{10}$  = Thermal Resistance Junction to Ambient (°C/W)

#### **Example**

An SC1458A is used to provide outputs of 2.5V, 150mA from LDOA and 1.8V, 200mA from LDOB. The input voltage is 4.2V, and the ambient temperature of the system is 60°C.

$$P_D = 0.15(4.2 - 2.5) + 0.2(4.2 - 1.8)$$

= 0.74W

and

$$T_1 = 60 + (0.74 \times 50) = 97^{\circ}C$$

Figure 3 shows that the power dissipation is within limits at  $T_{\Delta} = 60$ °C and calculation of  $T_{\perp}$  shows that it is within the specified limit of 150°C.

This means that operation of the SC1458 under these conditions is within the specified limits and the device would not require further thermal relief measures.

# **Applications Information (continued)**

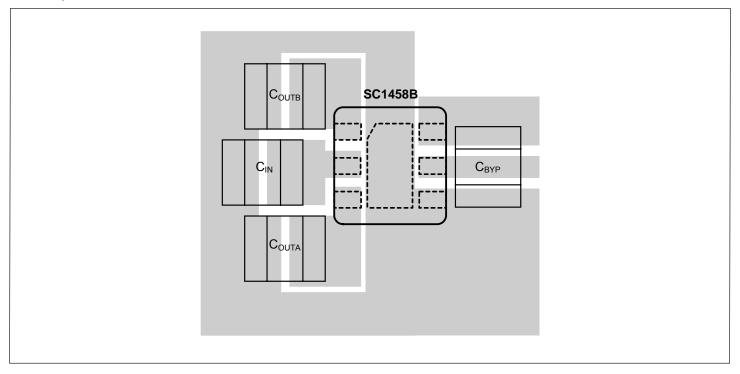

#### **PCB Layout Considerations**

While layout for linear devices is generally not as critical as for a switching application, careful attention to detail will ensure reliable operation.

- Attach the part to a large copper footprint, particularly the thermal pad on the underside of the device, to enable better heat transfer, particularly on PCBs where there are internal power and ground planes.

- Place the input, output, and bypass capacitors close to the device for optimal transient response and device behavior.

- Connect all ground connections directly to the ground plane whenever possible to minimize ground potential differences on the PCB.

- Ensure that the feedback resistors are placed as close as possible to the feedback pins.

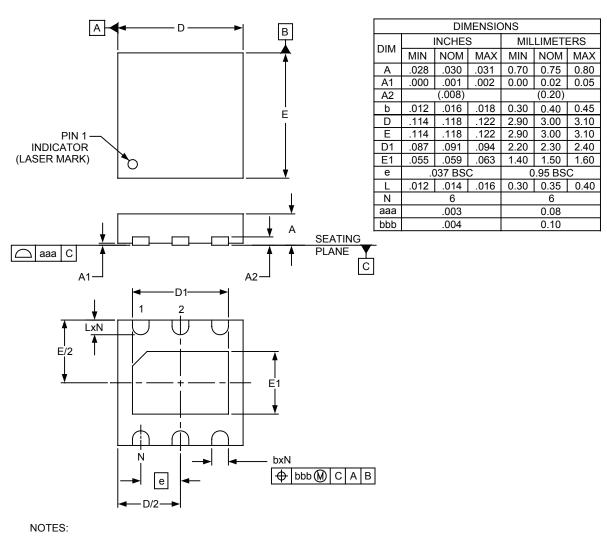

# Outline Drawing — MLPD-W6 3x3

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS TERMINALS.

- 3. REFERENCE JEDEC STANDARD VARIATION WEEA-2.

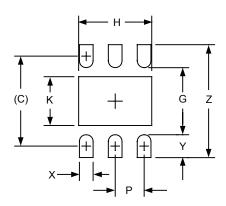

#### Land Pattern — MLPD-W6 3x3

|     | DIMENSIONS  |             |  |  |  |  |

|-----|-------------|-------------|--|--|--|--|

| DIM | INCHES      | MILLIMETERS |  |  |  |  |

| С   | (.116)      | (2.95)      |  |  |  |  |

| G   | .087        | 2.20        |  |  |  |  |

| Н   | .094        | 2.40        |  |  |  |  |

| K   | .063        | 1.60        |  |  |  |  |

| Р   | .037        | 0.95        |  |  |  |  |

| R   | .009        | 0.225       |  |  |  |  |

| Х   | .018        | 0.45        |  |  |  |  |

| Υ   | · .030 0.75 |             |  |  |  |  |

| Z   | .146        | 3.70        |  |  |  |  |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 3. THERMAL VIAS IN THE LAND PATTERN OF THE EXPOSED PAD SHALL BE CONNECTED TO A SYSTEM GROUND PLANE. FAILURE TO DO SO MAY COMPROMISE THE THERMAL AND/OR FUNCTIONAL PERFORMANCE OF THE DEVICE.

# **Contact Information**

Semtech Corporation

Power Mangement Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805) 498-2111 Fax: (805) 498-3804

www.semtech.com