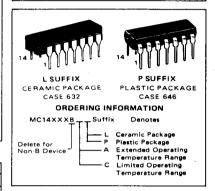

## MC14011 MC14011B

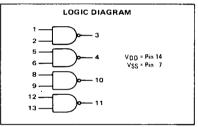

## QUAD 2-INPUT "NAND" GATE

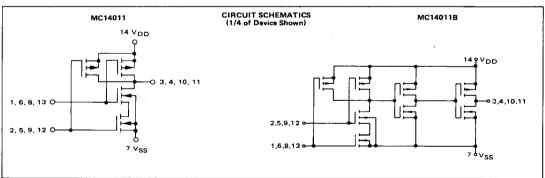

The MC14011 and MC14011B are constructed with P and N channel enhancement mode devices in a single monolithic structure (Complementary MOS). Their primary use is where low power dissipation and/or high noise immunity is desired.

- Quiescent Current = 0.5 nA typ/pkg @ 5 Vdc

- Noise Immunity = 45% of V<sub>DD</sub> typ

- Supply Voltage Range = 3.0 Vdc to 18 Vdc

- All Outputs Buffered (MC14011B only)

- Capable of Driving Two Low-power TTL Loads, One Low-power Schottky TTL Load or Two HTL Loads Over the Rated Temperature Range. (MC14011B only)

- Double Diode Protection on All Inputs

- Pin-for-Pin Replacements for CD4011A and CD4011B

## MAXIMUM RATINGS (Voltages referenced to VSS)

| Rating                                             | Symbol | Value                        | Unit |

|----------------------------------------------------|--------|------------------------------|------|

| DC Supply Voltage                                  | VDD    | -0.5 to +18                  | Vdc  |

| Input Voltage, All Inputs                          | Vin    | -0.5 to V <sub>DD</sub> +0.5 | Vdc  |

| DC Current Drain per Pin                           | 1      | 10                           | mAdc |

| Operating Temperature Range AL Device CL/CP Device | ТД     | -55 to +125<br>-40 to +85    | °C   |

| Storage Temperature Range                          | Tstg   | -65 to +150                  | °C   |

See the MC14001 data sheet for complete characteristics for the non-B device.

See the MC14001B data sheet for complete characteristics of the B-Series device.

## McMOS SSI

(LOW-POWER COMPLEMENTARY MOS)

QUAD 2-INPUT "NAND" GATE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper

operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leqslant (V_{in} \text{ or } V_{out}) \leqslant V_{DD}$ . Unused inputs must always be tied to an appropriate logic voltage level (e.g., either  $V_{SS} \text{ or } V_{DD}$ ).