## 36K, 64K, and 128K Serial EPROM Family

### FEATURES

- Operationally equivalent to Xilinx® XC1700 family

- Wide voltage range 3.0 V to 6.0 V

- Maximum read current 10 mA at 5.0 V

- Standby current 100  $\mu$ A typical

- Industry standard Synchronous Serial Interface/ 1 bit per rising edge of clock

- Full Static Operation

- Sequential Read/Program

- Cascadable Output Enable

- 10 MHz Maximum Clock Rate @ 5.0 Vdc

- Programmable Polarity on Hardware Reset

- Programming with industry standard EPROM programmers

- Electrostatic discharge protection > 4,000 volts

- 8-pin PDIP/SOIC and 20-pin PLCC packages

- Data Retention > 200 years

- Temperature ranges:

- Commercial: 0°C to +70°C

- Industrial: -40°C to +85°C

### DESCRIPTION

The Microchip Technology Inc. 37LV36/65/128 is a family of Serial OTP EPROM devices organized internally in a x32 configuration. The family also features a cascadable option for increased memory storage where needed. The 37LV36/65/128 is suitable for many applications in which look-up table information storage is desirable and provides full static operation in the 3.0V to 6.0V Vcc range. The devices also support the industry standard serial interface to the popular RAM-based Field Programmable Gate Arrays (FPGA). Advanced CMOS technology makes this an ideal bootstrap solution for today's high speed SRAM-based FPGAs. The 37LV36/65/128 family is available in the standard 8-pin plastic DIP, 8-pin SOIC and 20-pin PLCC packages.

| Device  | Bits    | Programming Word |

|---------|---------|------------------|

| 37LV36  | 36,288  | 1134 x 32        |

| 37LV65  | 65,536  | 2048 x 32        |

| 37LV128 | 131,072 | 4096 x 32        |

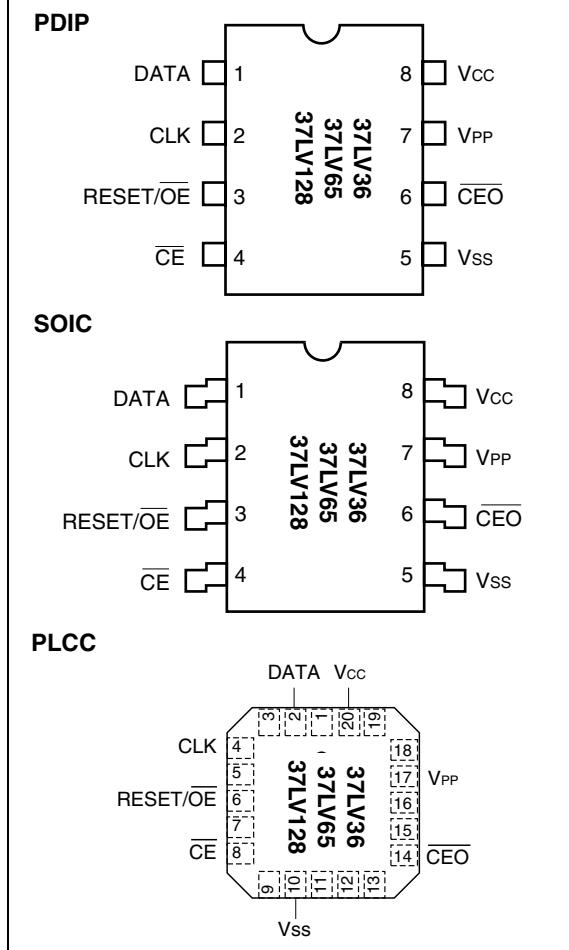

### PACKAGE TYPES

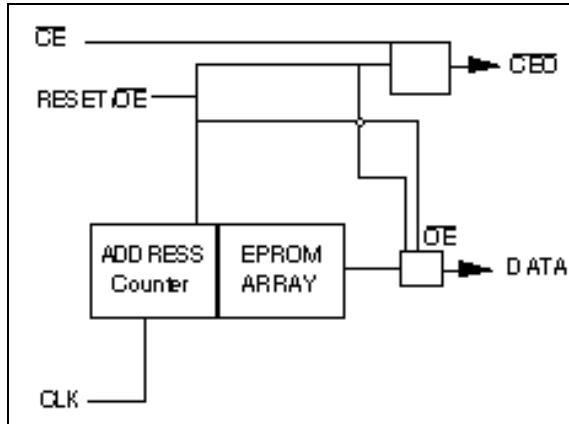

### BLOCK DIAGRAM

Xilinx is a registered trademark of Xilinx Corporation.

## 1.0 ELECTRICAL CHARACTERISTICS

### 1.1 Maximum Ratings\*

Vcc and input voltages w.r.t. Vss ..... -0.6V to +0.6V

VPP voltage w.r.t. Vss during programming ..... -0.6V to +14.0V

Output voltage w.r.t. Vss ..... -0.6V to Vcc +0.6V

Storage temperature ..... -65°C to +150°C

Ambient temp. with power applied..... -65°C to +125°C

Soldering temperature of leads (10 sec.) ..... +300°C

ESD protection on all pins .....  $\geq 4$  kV

\*Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 1-1: PIN FUNCTION TABLE

| Name             | Function                      | 8 | 20 |

|------------------|-------------------------------|---|----|

| DATA             | Data I/O                      | 1 | 2  |

| CLK              | Clock Input                   | 2 | 4  |

| RESET/OE         | Reset Input and Output Enable | 3 | 6  |

| $\overline{CE}$  | Chip Enable Input             | 4 | 8  |

| Vss              | Ground                        | 5 | 10 |

| $\overline{CEO}$ | Chip Enable Output            | 6 | 14 |

| VPP              | Programming Voltage Supply    | 7 | 17 |

| VCC              | +3.0V to 6.0V Power Supply    | 8 | 20 |

| Not Labeled      | Not utilized, not connected   |   |    |

TABLE 1-2: READ OPERATION DC CHARACTERISTICS

| Vcc = +3.0 to 6.0V<br>Commercial (C): Tamb = 0°C to +70°C<br>Industrial (I): Tamb = -40°C to +85°C                                                                       |                                   |                                 |                               |                       |                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------|-------------------------------|-----------------------|---------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                                                | Symbol                            | Min.                            | Max.                          | Units                 | Conditions                                                                                  |

| DATA, $\overline{CE}$ , $\overline{CEO}$ and Reset pins:<br>High level input voltage<br>Low level input voltage<br>High level output voltage<br>Low level output voltage | VIH<br>VIL<br>VOH1<br>VOH2<br>VOL | 2.0<br>-0.3<br>3.86<br>2.4<br>— | Vcc<br>0.8<br>V<br>2.4<br>.32 | V<br>V<br>V<br>V<br>V | $I_{OH} = -4$ mA Vcc $\geq 4.5$ V<br>$I_{OH} = -4$ mA Vcc $\geq 3.0$ V<br>$I_{OL} = 4.0$ mA |

| Input Leakage                                                                                                                                                            | ILI                               | -10                             | 10                            | $\mu$ A               | $V_{IN} = .1$ V to Vcc                                                                      |

| Output Leakage                                                                                                                                                           | ILO                               | -10                             | 10                            | $\mu$ A               | $V_{OUT} = .1$ V to Vcc                                                                     |

| Input Capacitance (all inputs/outputs)                                                                                                                                   | CINT                              | —                               | 10                            | pF                    | Tamb = 25°C; FCLK = 1 MHz (Note 1)                                                          |

| Operating Current                                                                                                                                                        | Icc Read                          | —                               | 10<br>2                       | mA<br>mA              | Vcc = 6.0V, CLK = 10 MHz<br>Vcc = 3.6V, CLK = 2.5 MHz<br>Outputs open                       |

| Standby Current                                                                                                                                                          | Iccs                              | —                               | 100<br>50                     | $\mu$ A<br>$\mu$ A    | Vcc = 6.0V, CE = 5.8V<br>Vcc = 3.6V, CE = 3.4V                                              |

Note 1: This parameter is initially characterized and not 100% tested.

## 2.0 DATA

### 2.1 Data I/O

Three-state DATA output for reading and input during programming.

## 3.0 CLK

### 3.1 Clock Input

Used to increment the internal address and bit counters for reading and programming.

## 4.0 RESET/OE

### 4.1 Reset Input and Output Enable

A LOW level on both the CE and RESET/OE inputs enables the data output driver. A HIGH level on RESET/OE resets both the address and bit counters. In the 37LVXXX, the logic polarity of this input is programmable as either RESET/OE or OE/RESET. This document describes the pin as RESET/OE although the opposite polarity is also possible. This option is defined and set at device program time.

## 5.0 CE

### 5.1 Chip Enable Input

CE is used for device selection. A LOW level on both CE and OE enables the data output driver. A HIGH level on CE disables both the address and bit counters and forces the device into a low power mode.

## 6.0 CEO

### 6.1 Chip Enable Output

This signal is asserted LOW on the clock cycle following the last bit read from the memory. It will stay LOW as long as CE and OE are both LOW. It will then follow CE until OE goes HIGH. Thereafter, CEO will stay HIGH until the entire EPROM is read again. This pin also used to sense the status of RESET polarity when Programming Mode is entered.

## 7.0 VPP

### 7.1 Programming Voltage Supply

Used to enter programming mode (+13 volts) and to program the memory (+13 volts). Must be connected directly to Vcc for normal Read operation. No overshoot above +14 volts is permitted.

## 8.0 CASCADING SERIAL EPROMS

Cascading Serial EPROMs provide additional memory for multiple FPGAs configured as a daisy-chain, or for future applications requiring larger configuration memories.

When the last bit from the first Serial EPROM is read, the next clock signal to the Serial EPROM asserts its CEO output LOW and disables its DATA line. The second Serial EPROM recognizes the LOW level on its CE input and enables its DATA output.

When configuration is complete, the address counters of all cascaded Serial EPROMs are reset if RESET goes LOW forcing the RESET/OE on each Serial EPROM to go HIGH. If the address counters are not to be reset upon completion, then the RESET/OE inputs can be tied to ground.

Additional logic may be required if cascaded memories are so large that the rippled chip enable is not fast enough to activate successive Serial EPROMs.

## 9.0 STANDBY MODE

The 37LVXXX enters a low-power Standby Mode whenever CE is HIGH. In Standby Mode, the Serial EPROM consumes less than 100  $\mu$ A of current. The output will remain in a high-impedance state regardless of the state of the OE input.

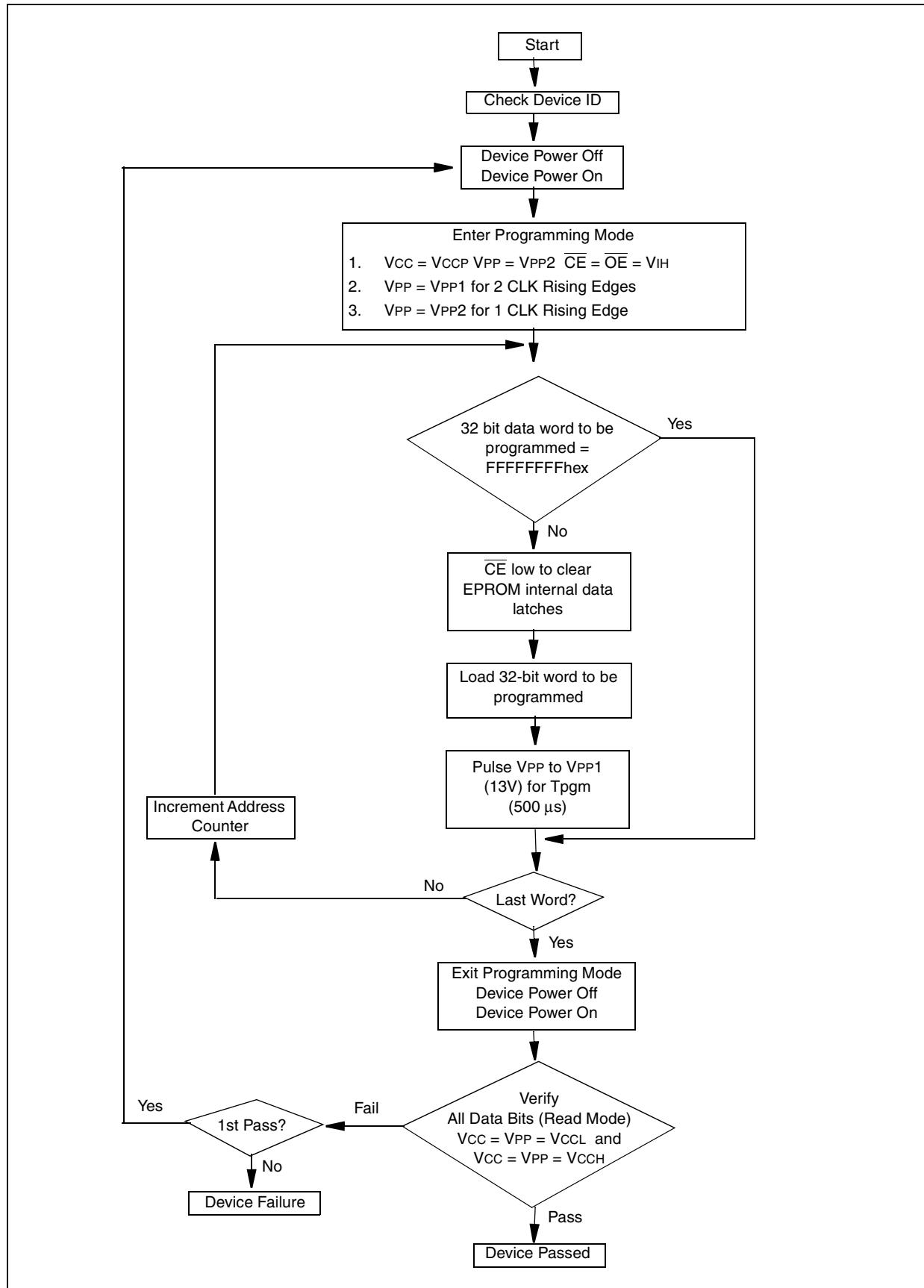

## 10.0 PROGRAMMING MODE

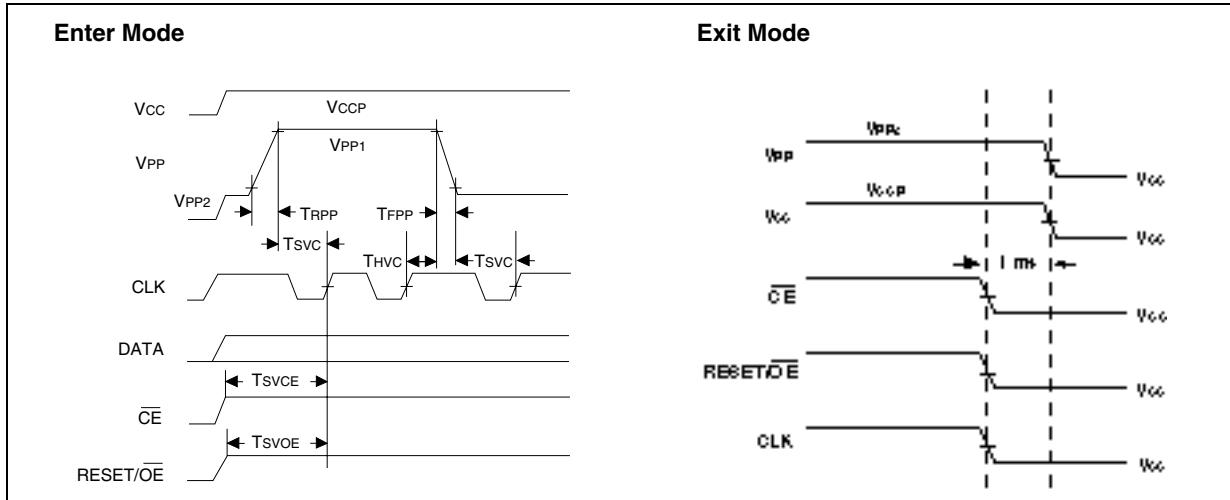

Programming Mode is entered by holding VPP HIGH (+13 volts) for two clock edges and then holding VPP = VDD for one clock edge. Programming mode is exited by driving a LOW on both CE and OE and then removing power from the device. Figures 4 through 7 show the programming algorithm.

## 11.0 37LVXXX RESET POLARITY

The 37LVXXX lets the user choose the reset polarity as either RESET/OE or OE/RESET. Any third-party commercial programmer should prompt the user for the desired reset polarity.

The programming of the overflow word should be handled transparently by the EPROM programmer; it is mentioned here as supplemental information only.

The polarity is programmed into the first overflow word location, maximum address+1. 00000000 in these locations makes the reset active LOW, FFFFFFFF in these locations makes the reset active HIGH. The default condition is RESET active HIGH.

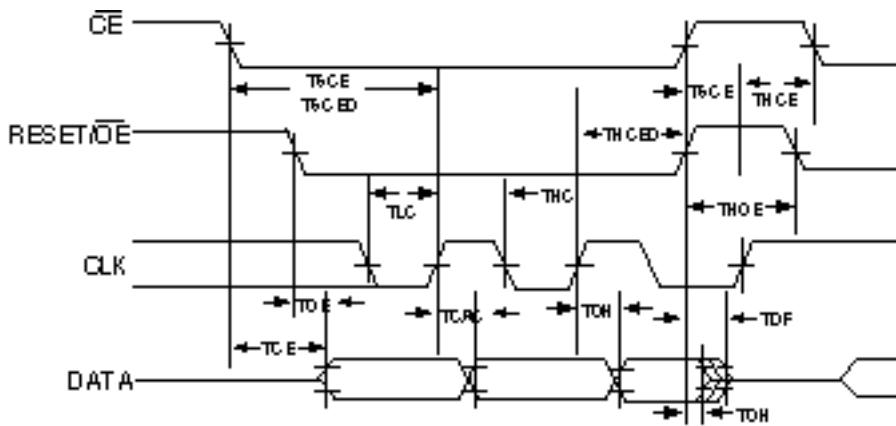

FIGURE 11-1: READ CHARACTERISTICS TIMING

TABLE 11-1: READ CHARACTERISTICS

| Symbol  | Parameter                                                            | Limits $3.0V \leq V_{cc} \leq 6.0V$ |      | Limits $4.5V \leq V_{cc} \leq 6.0V$ |      | Units | Conditions |

|---------|----------------------------------------------------------------------|-------------------------------------|------|-------------------------------------|------|-------|------------|

|         |                                                                      | Min.                                | Max. | Min.                                | Max. |       |            |

| TOE     | $\overline{OE}$ to Data Delay                                        | —                                   | 45   | —                                   | 45   | ns    |            |

| TCE     | $\overline{CE}$ to Data Delay                                        | —                                   | 60   | —                                   | 50   | ns    |            |

| TCAC    | CLK to Data Delay                                                    | —                                   | 200  | —                                   | 60   | ns    |            |

| TOH     | Data Hold from $\overline{CE}$ , $\overline{OE}$ or CLK              | 0                                   | —    | 0                                   | —    | ns    |            |

| TDF     | $\overline{CE}$ or $\overline{OE}$ to Data Float Delay               | —                                   | 50   | —                                   | 50   | ns    | Notes 1, 2 |

| TLC     | CLK Low Time                                                         | 100                                 | —    | 25                                  | —    | ns    |            |

| THC     | CLK High Time                                                        | 100                                 | —    | 25                                  | —    | ns    |            |

| TSCE    | $\overline{CE}$ Set up Time to CLK<br>(to guarantee proper counting) | 40                                  | —    | 25                                  | —    | ns    | Note 1     |

| TSCED   | $\overline{CE}$ setup time to CLK<br>(to guarantee proper DATA read) | 100                                 | —    | 80                                  | —    | ns    |            |

| THCE    | $\overline{CE}$ Hold Time to CLK<br>(to guarantee proper counting)   | 0                                   | —    | 0                                   | —    | ns    | Note 1     |

| THCED   | $\overline{CE}$ hold time to CLK<br>(to guarantee proper DATA read)  | 50                                  | —    | 0                                   | —    | ns    |            |

| THO E   | $\overline{OE}$ High Time<br>(Guarantees counters are Reset)         | 100                                 | —    | 20                                  | —    | ns    |            |

| CLK max | Clock Frequency                                                      | —                                   | 2.5  | —                                   | 10   | MHz   |            |

Note 1: This parameter is periodically sampled and not 100% tested.

2: Float delays are measured with output pulled through  $1k\Omega$  to  $V_{LOAD} = V_{cc}/2$ .

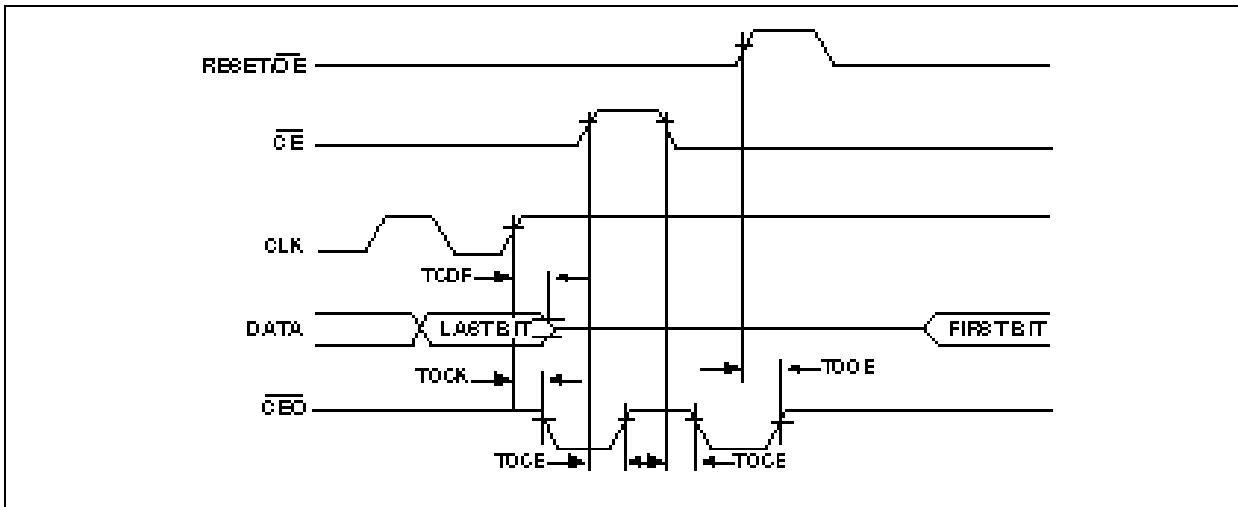

FIGURE 11-2: READ CHARACTERISTICS AT END OF ARRAY TIMING

TABLE 11-2: READ CHARACTERISTICS AT END OF ARRAY

| Symbol | Parameter                                 | Limits $3.0V \leq V_{cc} \leq 6.0V$ |      | Limits $4.5V \leq V_{cc} \leq 6.0V$ |      | Units | Conditions |

|--------|-------------------------------------------|-------------------------------------|------|-------------------------------------|------|-------|------------|

|        |                                           | Min.                                | Max. | Min.                                | Max. |       |            |

| TCDF   | CLK to Data Float Delay                   | —                                   | 50   | —                                   | 50   | ns    | Notes 1, 2 |

| TOCK   | CLK to $\overline{CEO}$ Delay             | —                                   | 65   | —                                   | 40   | ns    |            |

| TOCE   | $\overline{CE}$ to $\overline{CEO}$ Delay | —                                   | 45   | —                                   | 40   | ns    |            |

| TOOE   | RESET/OE to $\overline{CEO}$ Delay        | —                                   | 45   | —                                   | 40   | ns    |            |

Note 1: This parameter is periodically sampled and not 100% tested.

2: Float delays are measured with output pulled through  $1k\Omega$  to  $V_{LOAD} = V_{cc}/2$ .

**TABLE 11-3: PIN ASSIGNMENTS IN THE PROGRAMMING MODE**

| DIP/SOIC Pin | PLCC Pin | Name       | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|----------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | 2        | DATA       | I/O | The rising edge of the clock shifts a data word in or out of the EPROM one bit at a time.                                                                                                                                                                                                                                                                                                                  |

| 2            | 4        | CLK        | I   | Clock Input. Used to increment the internal address/word counter for reading and programming operation.                                                                                                                                                                                                                                                                                                    |

| 3            | 6        | RESET/OE   | I   | The rising edge of CLK shifts a data word into the EPROM when <u>CE</u> and <u>OE</u> are HIGH; it shifts a data word out of the EPROM when <u>CE</u> is LOW and <u>OE</u> is HIGH. The address/word counter is incremented on the rising edge of CLK while <u>CE</u> is held HIGH and <u>OE</u> is held LOW.<br><br>Note 1: Any modified polarity of the RESET/OE pin is ignored in the programming mode. |

| 4            | 8        | <u>CE</u>  | I   | The rising edge of CLK shifts a data word into the EPROM when <u>CE</u> and <u>OE</u> are HIGH; it shifts a data word out of the EPROM when <u>CE</u> is LOW and <u>OE</u> is HIGH. The address/word counter is incremented on the rising edge of CLK while <u>CE</u> is held HIGH and <u>OE</u> is held LOW.                                                                                              |

| 5            | 10       | Vss        |     | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                |

| 6            | 14       | <u>CEO</u> | O   | The polarity of the RESET/OE pin can be read by sensing the CEO pin.<br><br>Note 1: The polarity of the RESET/OE pin is ignored while in the Programming Mode. In final verification, this pin must be monitored to go LOW one clock cycle after the last data bit has been read.                                                                                                                          |

| 7            | 17       | VPP        |     | Programming Voltage Supply. Programming Mode is entered by holding <u>CE</u> and <u>OE</u> HIGH and VPP at VPP1 for two rising clock edges and then lowering VPP to VPP2 for one more rising clock edge. A word is programmed by strobing the device with VPP for the duration TPGM. VPP must be tied to Vcc for normal read operation.                                                                    |

| 8            | 20       | Vcc        |     | +5 V power supply input.                                                                                                                                                                                                                                                                                                                                                                                   |

TABLE 11-4: DC PROGRAMMING SPECIFICATIONS

| Symbol           | Parameter                                                    | Ambient Temperature: Tamb = 25°C ±5°C | Limits           |                     | Units |

|------------------|--------------------------------------------------------------|---------------------------------------|------------------|---------------------|-------|

|                  |                                                              |                                       | Min.             | Max.                |       |

| V <sub>CCP</sub> | Supply voltage during programming                            |                                       | 5.0              | 6.0                 | V     |

| V <sub>IL</sub>  | Low-level input voltage                                      |                                       | 0.0              | 0.5                 | V     |

| V <sub>IH</sub>  | High-level input voltage                                     |                                       | 2.4              | V <sub>CC</sub>     | V     |

| V <sub>OL</sub>  | Low-level output voltage                                     |                                       | —                | 0.4                 | V     |

| V <sub>OH</sub>  | High-level output voltage                                    |                                       | 3.7              | —                   | V     |

| V <sub>PP1</sub> | Programming voltage*                                         |                                       | 12.5             | 13.5                | V     |

| V <sub>PP2</sub> | Programming Mode access voltage                              |                                       | V <sub>CCP</sub> | V <sub>CCP</sub> +1 | V     |

| I <sub>PP</sub>  | Supply current in Programming Mode                           |                                       | —                | 100                 | mA    |

| I <sub>L</sub>   | Input or output leakage current                              |                                       | -10              | 10                  | µA    |

| V <sub>CCL</sub> | First pass Low-level supply voltage for final verification   |                                       | 2.8              | 3.0                 | V     |

| V <sub>CCH</sub> | Second pass High-level supply voltage for final verification |                                       | 6.4              | 6.6                 | V     |

\* No overshoot is permitted on this signal. V<sub>PP</sub> must not be allowed to exceed 14 volts.

TABLE 11-5: AC PROGRAMMING SPECIFICATIONS (SEE NOTE 2)

| Symbol            | Parameter                                                   | Limits |      | Units | Conditions |

|-------------------|-------------------------------------------------------------|--------|------|-------|------------|

|                   |                                                             | Min.   | Max. |       |            |

| T <sub>RPP</sub>  | 10% to 90% Rise Time of V <sub>PP</sub>                     | 1      |      | µs    | Note 1     |

| T <sub>FPP</sub>  | 90% to 10% Fall Time of V <sub>PP</sub>                     | 1      |      | µs    | Note 1     |

| T <sub>PGM</sub>  | V <sub>PP</sub> Programming Pulse Width                     | .50    | 1.05 | ms    |            |

| T <sub>SVC</sub>  | V <sub>PP</sub> Setup to CLK for Entering Programming Mode  | 100    |      | ns    | Note 1     |

| T <sub>SVCE</sub> | CE Setup to CLK for Entering Programming Mode               | 100    |      | ns    | Note 1     |

| T <sub>SVOE</sub> | OE Setup to CLK for Entering Programming Mode               | 100    |      | ns    | Note 1     |

| T <sub>HVC</sub>  | V <sub>PP</sub> Hold from CLK for Entering Programming Mode | 300    |      | ns    | Note 1     |

| T <sub>SDP</sub>  | Data Setup to CLK for Programming                           | 50     |      | ns    |            |

| T <sub>HDH</sub>  | Data Hold from CLK for Programming                          | 0      |      | ns    |            |

| T <sub>LC</sub>   | CE Low time to clear data latches                           | 100    |      | ns    |            |

| T <sub>SCC</sub>  | CE Setup to CLK for Programming/Verifying                   | 100    |      | ns    |            |

| T <sub>SIC</sub>  | OE Setup to CLK for Incrementing Address Counter            | 100    |      | ns    |            |

| T <sub>HIC</sub>  | OE Hold from CLK for Incrementing Address Counter           | 0      |      | ns    |            |

| T <sub>HOV</sub>  | OE Hold from V <sub>PP</sub>                                | 200    |      | ns    | Note 1     |

| T <sub>PCAC</sub> | CLK to Data Valid                                           |        | 400  | ns    |            |

| T <sub>POH</sub>  | Data Hold from CLK                                          | 0      |      | ns    |            |

| T <sub>PC</sub>   | CE Low to Data Valid                                        |        | 250  | ns    |            |

**Note 1:** This parameter is periodically sampled and not 100% tested.

**Note 2:** While in Programming Mode, CE should only be changed while OE is HIGH and has been HIGH for 200 ns, and OE should only be changed while CE is HIGH and has been HIGH for 200 ns.

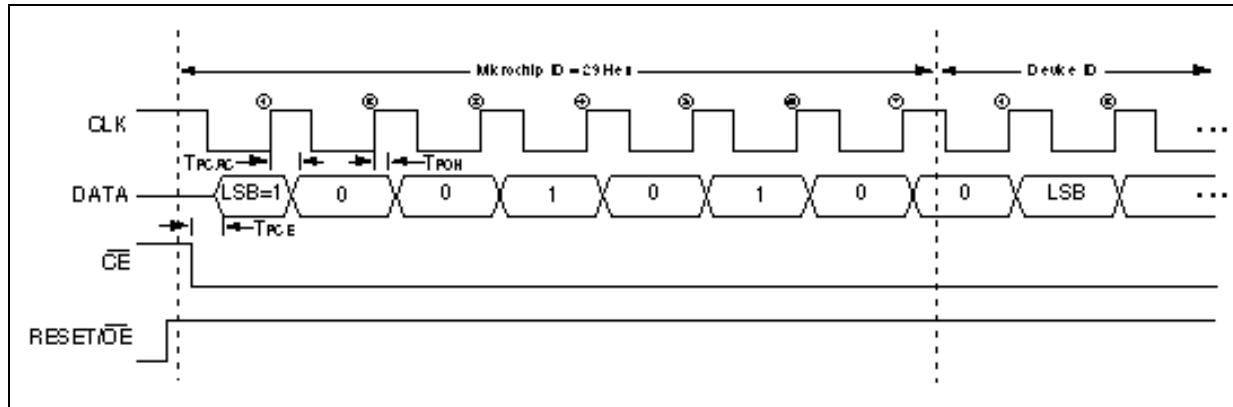

FIGURE 11-3: ENTER AND EXIT PROGRAMMING MODES

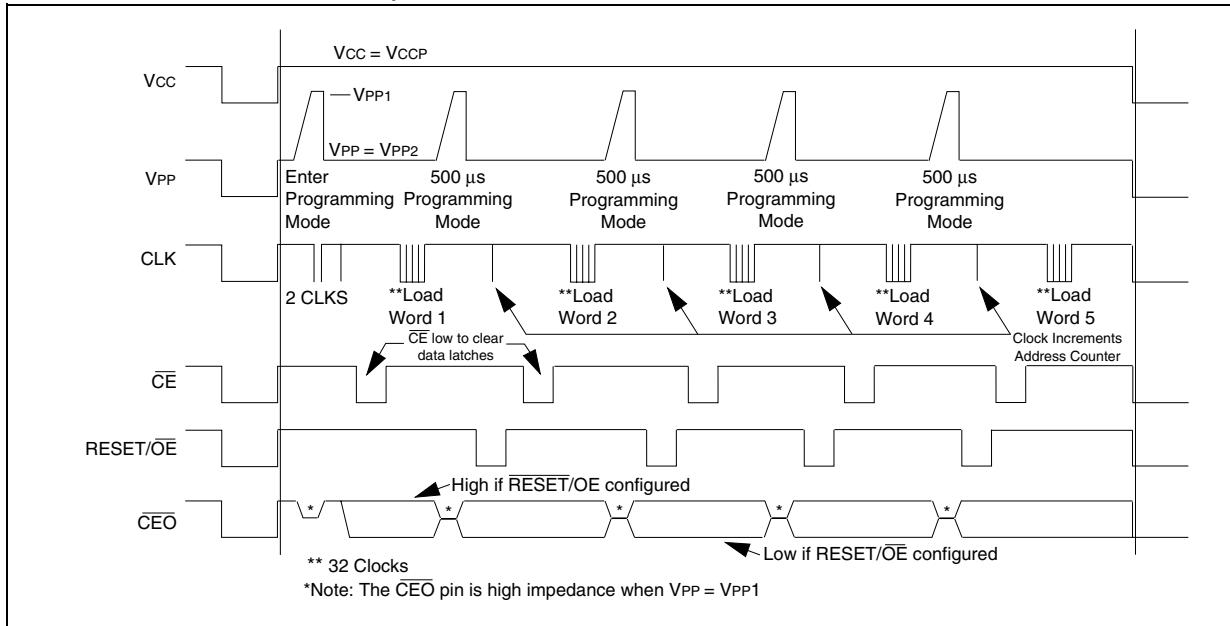

FIGURE 11-4: PROGRAMMING CYCLE OVERVIEW (NO VERIFY UNTIL ENTIRE ARRAY IS PROGRAMMED)

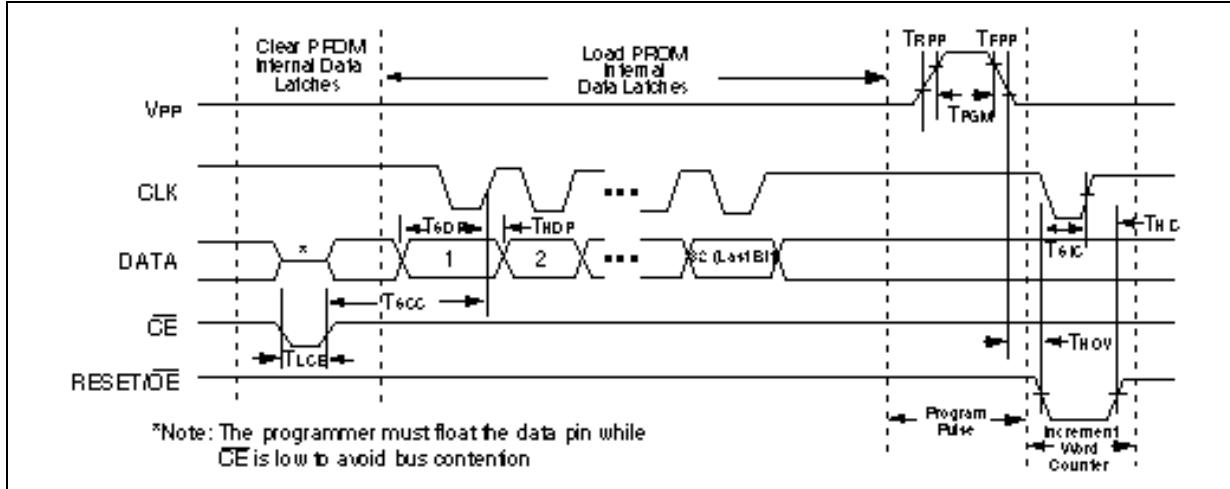

FIGURE 11-5: DETAILS OF PROGRAM CYCLE

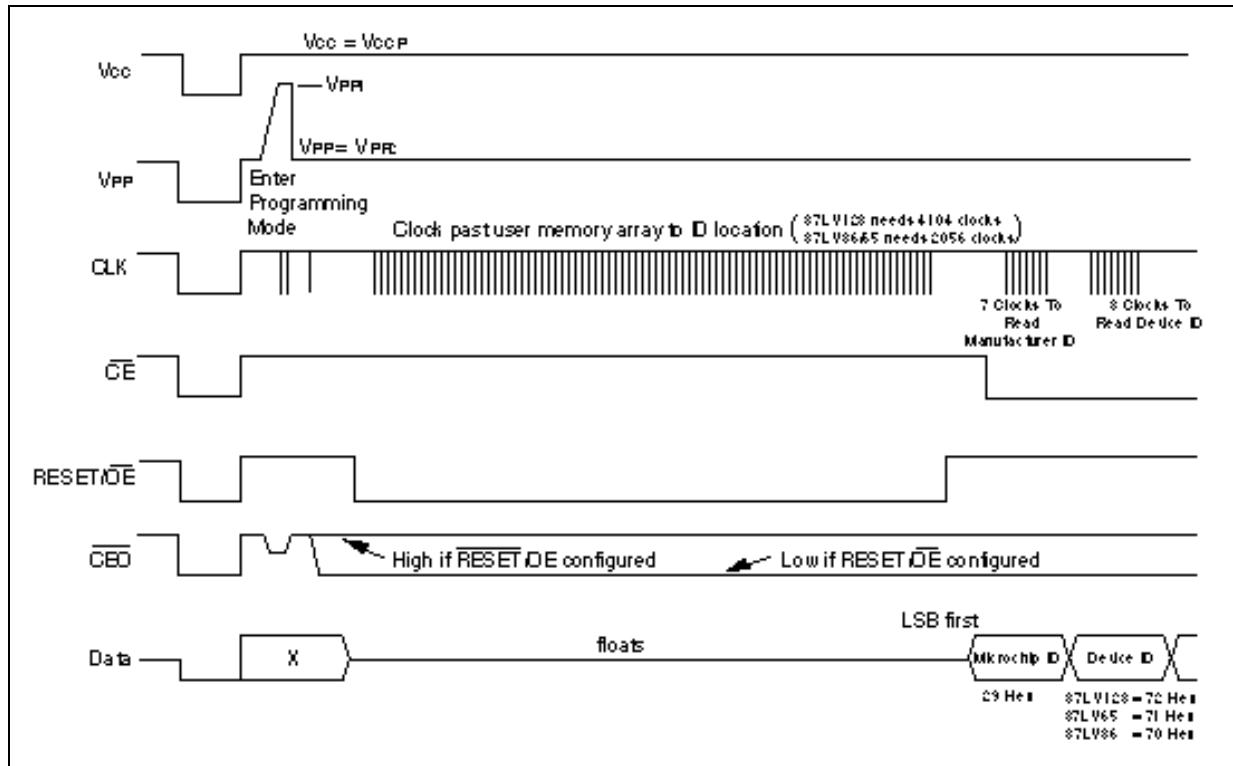

FIGURE 11-6: READ MANUFACTURER AND DEVICE ID OVERVIEW

FIGURE 11-7: DETAILS OF READ MANUFACTURER AND DEVICE ID

FIGURE 11-8: 37LVXXX PROGRAMMING SPECIFICATIONS

## **37LV36/65/128 Product Identification System**

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.

| <b>37LV36/65/128</b> | <b>-</b> | <b>I</b> | <b>T</b> | <b>/P</b> |                                                                                                                        |

|----------------------|----------|----------|----------|-----------|------------------------------------------------------------------------------------------------------------------------|

|                      |          |          |          |           | <b>Package:</b>                                                                                                        |

|                      |          |          |          |           | P = Plastic DIP, 8 lead<br>SN = Plastic SOIC (150 mil Body), 8 lead<br>L = Plastic Leaded Chip Carrier (PLCC), 20 lead |

|                      |          |          |          |           | <b>Temperature Range:</b>                                                                                              |

|                      |          |          |          |           | Blank = 0°C to +70°C<br>I = -40°C to +85°C                                                                             |

|                      |          |          |          |           | <b>Shipping:</b>                                                                                                       |

|                      |          |          |          |           | Blank = Tube<br>T = Tape and Reel                                                                                      |

|                      |          |          |          |           | <b>Device:</b>                                                                                                         |

|                      |          |          |          |           | 37LV128 128K Serial EPROM<br>37LV65 64K Serial EPROM<br>37LV36 36K Serial EPROM                                        |

---

---

**Note the following details of the code protection feature on PICmicro® MCUs.**

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

---

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# MICROCHIP

## WORLDWIDE SALES AND SERVICE

### AMERICAS

#### Corporate Office

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277

Technical Support: 480-792-7627

Web Address: <http://www.microchip.com>

#### Rocky Mountain

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B

Atlanta, GA 30350

Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

2 Lan Drive, Suite 120

Westford, MA 01886

Tel: 978-692-3848 Fax: 978-692-3821

#### Chicago

333 Pierce Road, Suite 180

Itasca, IL 60143

Tel: 630-285-0071 Fax: 630-285-0075

#### Dallas

4570 Westgrove Drive, Suite 160

Addison, TX 75001

Tel: 972-818-7423 Fax: 972-818-2924

#### Detroit

Tri-Atria Office Building

32255 Northwestern Highway, Suite 190

Farmington Hills, MI 48334

Tel: 248-538-2250 Fax: 248-538-2260

#### Kokomo

2767 S. Albright Road

Kokomo, Indiana 46902

Tel: 765-864-8360 Fax: 765-864-8387

#### Los Angeles

18201 Von Karman, Suite 1090

Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338

#### New York

150 Motor Parkway, Suite 202

Hauppauge, NY 11788

Tel: 631-273-5305 Fax: 631-273-5335

#### San Jose

Microchip Technology Inc.

2107 North First Street, Suite 590

San Jose, CA 95131

Tel: 408-436-7950 Fax: 408-436-7955

#### Toronto

6285 Northam Drive, Suite 108

Mississauga, Ontario L4V 1X5, Canada

Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

#### Australia

Microchip Technology Australia Pty Ltd

Suite 22, 41 Rawson Street

Epping 2121, NSW

Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

#### China - Beijing

Microchip Technology Consulting (Shanghai)

Co., Ltd., Beijing Liaison Office

Unit 915

Bei Hai Wan Tai Bldg.

No. 6 Chaoyangmen Beidajie

Beijing, 100027, No. China

Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Chengdu

Microchip Technology Consulting (Shanghai)

Co., Ltd., Chengdu Liaison Office

Rm. 2401, 24th Floor,

Ming Xing Financial Tower

No. 88 TIDU Street

Chengdu 610016, China

Tel: 86-28-6766200 Fax: 86-28-6766599

#### China - Fuzhou

Microchip Technology Consulting (Shanghai)

Co., Ltd., Fuzhou Liaison Office

Unit 28F, World Trade Plaza

No. 71 Wusi Road

Fuzhou 350001, China

Tel: 86-591-7503506 Fax: 86-591-7503521

#### China - Shanghai

Microchip Technology Consulting (Shanghai)

Co., Ltd.

Room 701, Bldg. B

Far East International Plaza

No. 317 Xian Xia Road

Shanghai, 200051

Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### China - Shenzhen

Microchip Technology Consulting (Shanghai)

Co., Ltd., Shenzhen Liaison Office

Rm. 1315, 13/F, Shenzhen Kerry Centre,

Renmin Lu

Shenzhen 518001, China

Tel: 86-755-2350361 Fax: 86-755-2366086

#### Hong Kong

Microchip Technology Hongkong Ltd.

Unit 901-6, Tower 2, Metropiazza

223 Hing Fong Road

Kwai Fong, N.T., Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

#### India

Microchip Technology Inc.

India Liaison Office

Divyasree Chambers

1 Floor, Wing A (A3/A4)

No. 11, O'Shaugnessy Road

Bangalore, 560 025, India

Tel: 91-80-2290061 Fax: 91-80-2290062

### Japan

Microchip Technology Japan K.K.

Benex S-1 6F

3-18-20, Shinyokohama

Kohoku-Ku, Yokohama-shi

Kanagawa, 222-0033, Japan

Tel: 81-45-471-6166 Fax: 81-45-471-6122

### Korea

Microchip Technology Korea

168-1, Youngbo Bldg. 3 Floor

Samsung-Dong, Kangnam-Ku

Seoul, Korea 135-882

Tel: 82-2-554-7200 Fax: 82-2-558-5934

### Singapore

Microchip Technology Singapore Pte Ltd.

200 Middle Road

#07-02 Prime Centre

Singapore, 188980

Tel: 65-334-8870 Fax: 65-334-8850

### Taiwan

Microchip Technology Taiwan

11F-3, No. 207

Tung Hua North Road

Taipei, 105, Taiwan

Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

### EUROPE

#### Denmark

Microchip Technology Nordic ApS

Regus Business Centre

Lautrup høj 1-3

Ballerup DK-2750 Denmark

Tel: 45 4420 9895 Fax: 45 4420 9910

#### France

Microchip Technology SARL

Parc d'Activité du Moulin de Massy

43 Rue du Saule Trapu

Bâtiment A - 1er Etage

91300 Massy, France

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

#### Germany

Microchip Technology GmbH

Gustav-Heinemann Ring 125

D-81739 Munich, Germany

Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

#### Italy

Microchip Technology SRL

Centro Direzionale Colleoni

Palazzo Taurus 1 V. Le Colleoni 1

20041 Agrate Brianza

Milan, Italy

Tel: 39-039-65791-1 Fax: 39-039-6899883

#### United Kingdom

Arizona Microchip Technology Ltd.

505 Eskdale Road

Winnersh Triangle

Wokingham

Berkshire, England RG41 5TU

Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/18/02