# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

## General Description

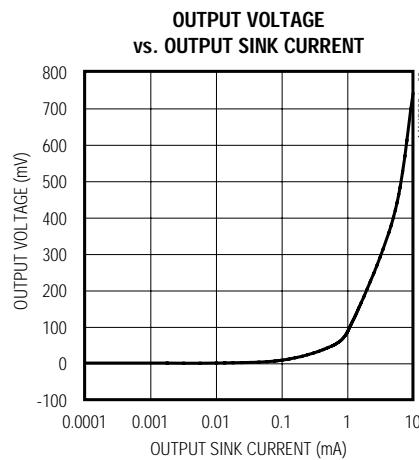

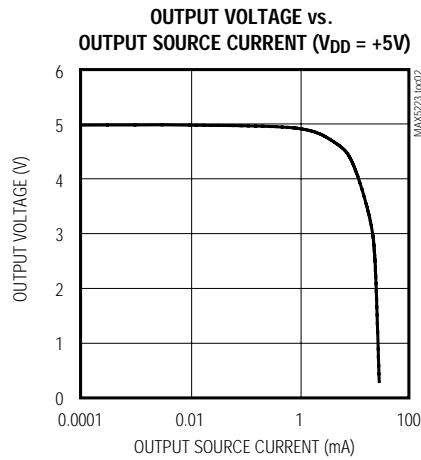

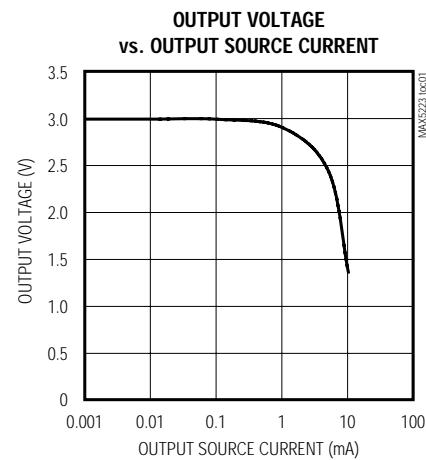

The MAX5223 contains two 8-bit, buffered, voltage output digital-to-analog converters (DAC A and DAC B) in a small 8-pin SOT23 package. DAC outputs can source and sink 1mA to within 100mV of ground and VDD. The MAX5223 operates with a single +2.7V to +5.5V supply.

The device uses a 3-wire serial interface, which operates at clock rates up to 25MHz and is compatible with SPI™, QSPI™, and MICROWIRE™ interface standards. The serial input shift register is 16 bits long and consists of 8 bits of DAC input data and 8 bits for DAC selection and shutdown control. DAC registers can be loaded independently or in parallel at the positive edge of CS.

The MAX5223's ultra-low power consumption and tiny 8-pin SOT23 package make it ideal for portable and battery-powered applications. Supply current is a low 100 $\mu$ A and drops below 1 $\mu$ A in shutdown mode. In addition, the reference input is disconnected from the REF pin during shutdown, which reduces the system's total power consumption.

## Applications

- Digital Gain and Offset Adjustment

- Programmable Current Source

- Programmable Voltage Source

- Power Amp Bias Control

- VCO Tuning

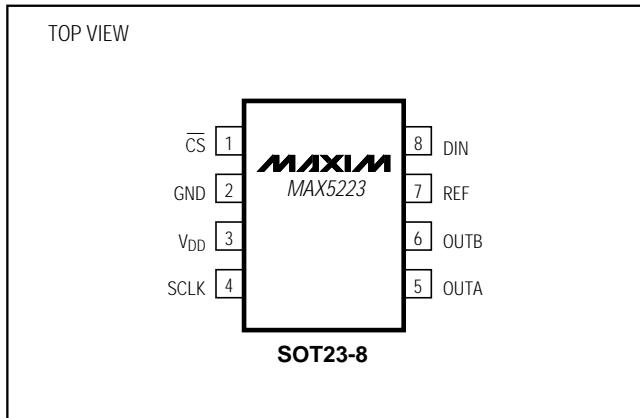

## Pin Configuration

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

## Features

- ♦ Tiny 8-Pin SOT23 Package (3mm x 3mm)

- ♦ Low Power Consumption

- 100 $\mu$ A Operating Current

- <1 $\mu$ A Shutdown Current

- ♦ +2.7V to +5.5V Single-Supply Operation

- ♦ Dual Buffered Voltage Output

- ♦ Programmable Shutdown Mode

- ♦ 25MHz, 3-Wire Serial Interface

- ♦ SPI, QSPI, and MICROWIRE-Compatible

## Ordering Information

| PART         | TEMP. RANGE    | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX5223EKA-T | -40°C to +85°C | 8 SOT23     |

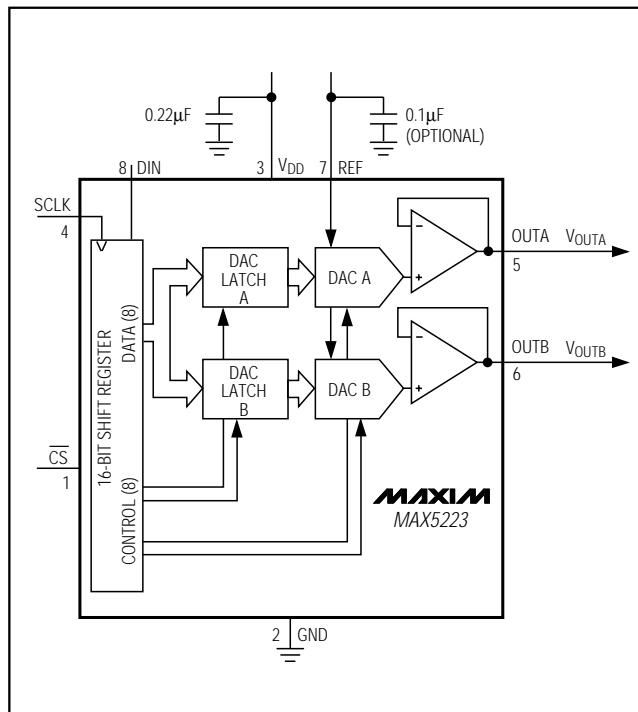

## Functional Diagram

MAX5223

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

## ABSOLUTE MAXIMUM RATINGS

$V_{DD}$  to GND ..... -0.3V to +6V

All Other Pins to GND (Note 1) ..... -0.3V to ( $V_{DD}$  + 0.3V)

Continuous Power Dissipation ( $T_A = +70^\circ\text{C}$ ) ..... 8-Pin SOT23 (derate 8.7mW/°C above +70°C) ..... 696mW

Operating Temperature Range ..... -40°C to +85°C

Junction Temperature ..... +150°C

Storage Temperature Range ..... -65°C to +150°C

Lead Temperature (soldering, 10s) ..... +300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

( $V_{DD} = +2.7\text{V}$  to  $+5.5\text{V}$ ,  $\text{REF} = V_{DD}$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                                  | SYMBOL     | CONDITIONS                                                                                              | MIN                 | TYP       | MAX     | UNITS                        |

|--------------------------------------------|------------|---------------------------------------------------------------------------------------------------------|---------------------|-----------|---------|------------------------------|

| <b>STATIC PERFORMANCE</b>                  |            |                                                                                                         |                     |           |         |                              |

| Resolution                                 | N          |                                                                                                         | 8                   |           |         | Bits                         |

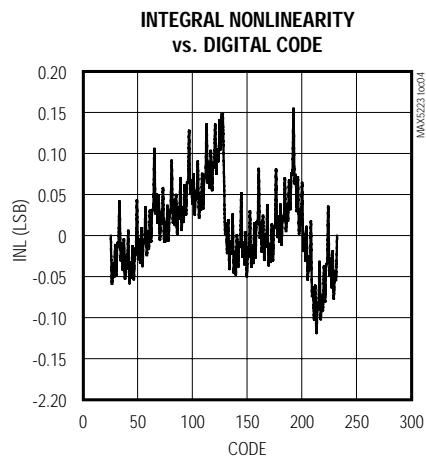

| Integral Nonlinearity                      | INL        | $I_{LOAD} = 250\mu\text{A}$ (Note 2)                                                                    |                     | $\pm 0.3$ | $\pm 1$ | LSB                          |

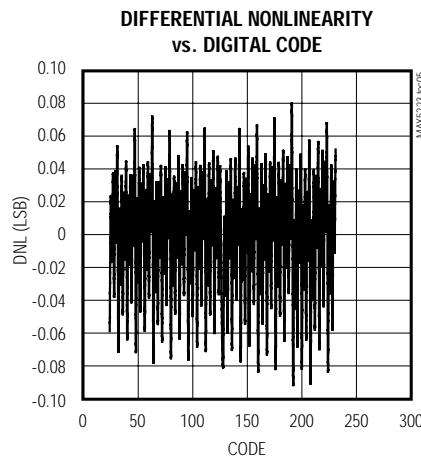

| Differential Nonlinearity                  | DNL        | Guaranteed monotonic, $I_{LOAD} = 250\mu\text{A}$ (Note 2)                                              |                     | $\pm 0.2$ | $\pm 1$ | LSB                          |

| Total Unadjusted Error                     | TUE        |                                                                                                         |                     | $\pm 1$   |         | LSB                          |

| Zero-Code Offset                           | $V_{ZS}$   |                                                                                                         |                     | 10        |         | mV                           |

| Zero-Code Temperature Coefficient          | $TC_{VZS}$ |                                                                                                         |                     | 100       |         | $\mu\text{V}/^\circ\text{C}$ |

| Power Supply Rejection Ratio               | PSRR       | $4.5\text{V} \leq V_{DD} \leq 5.5\text{V}$ , $V_{REF} = 4.096\text{V}$ ,<br>$I_{LOAD} = 250\mu\text{A}$ |                     | 1         |         | mV/V                         |

|                                            |            | $2.7\text{V} \leq V_{DD} \leq 3.6\text{V}$ , $V_{REF} = 2.4\text{V}$ ,<br>$I_{LOAD} = 250\mu\text{A}$   |                     | 1         |         |                              |

| <b>REFERENCE INPUT</b>                     |            |                                                                                                         |                     |           |         |                              |

| Reference Input Voltage Range              |            |                                                                                                         | GND                 | $V_{DD}$  |         | V                            |

| Reference Input Capacitance                |            |                                                                                                         |                     | 25        |         | pF                           |

| Reference Input Resistance                 | $R_{REF}$  | (Note 3)                                                                                                | 8                   | 16        |         | $\text{k}\Omega$             |

| Reference Input Resistance (Shutdown Mode) |            |                                                                                                         |                     | 50        |         | $\text{M}\Omega$             |

| <b>DAC OUTPUTS</b>                         |            |                                                                                                         |                     |           |         |                              |

| Output Voltage Range                       |            | $I_{LOAD} = 0$                                                                                          | 0                   | REF       |         | V                            |

| Capacitive Load at $OUT_-$                 |            |                                                                                                         |                     |           | 100     | pF                           |

| Output Resistance                          |            |                                                                                                         |                     |           | 500     | $\Omega$                     |

| <b>DIGITAL INPUTS</b>                      |            |                                                                                                         |                     |           |         |                              |

| Input High Voltage                         | $V_{IH}$   |                                                                                                         | $0.7 \times V_{DD}$ |           |         | V                            |

| Input Low Voltage                          | $V_{IL}$   |                                                                                                         | $0.3 \times V_{DD}$ |           |         | V                            |

| Input Current                              | $I_{IN}$   | $V_{IN} = 0$ or $V_{DD}$                                                                                | 0.1                 | $\pm 10$  |         | $\mu\text{A}$                |

| Input Capacitance                          | $C_{IN}$   | (Note 4)                                                                                                |                     | 10        |         | pF                           |

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{DD} = +2.7V$  to  $+5.5V$ ,  $REF = V_{DD}$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .)

| PARAMETER                         | SYMBOL   | CONDITIONS                                    | MIN  | TYP | MAX | UNITS                    |

|-----------------------------------|----------|-----------------------------------------------|------|-----|-----|--------------------------|

| <b>DYNAMIC PERFORMANCE</b>        |          |                                               |      |     |     |                          |

| Voltage Output Slew Rate          | SR       | $C_L = 100\text{pF}$                          | 0.15 |     |     | $\text{V}/\mu\text{s}$   |

| Voltage Output Settling Time      |          | To $\pm 1/2\text{LSB}$ , $C_L = 100\text{pF}$ | 50   |     |     | $\mu\text{s}$            |

| Digital Feedthrough and Crosstalk |          | All zeros to all ones                         | 0.25 |     |     | $\text{nV}\cdot\text{s}$ |

| <b>POWER SUPPLY</b>               |          |                                               |      |     |     |                          |

| Supply Voltage Range              | $V_{DD}$ |                                               | 2.7  | 5.5 |     | V                        |

| Supply Current                    | $I_{DD}$ | All inputs = 0                                | 150  | 275 |     | $\mu\text{A}$            |

|                                   |          | $V_{DD} = +3.6\text{V}$                       | 100  | 220 |     |                          |

| Shutdown Supply Current           |          | $V_{DD} = +5.5\text{V}$                       | 0.6  |     |     | $\mu\text{A}$            |

## TIMING CHARACTERISTICS

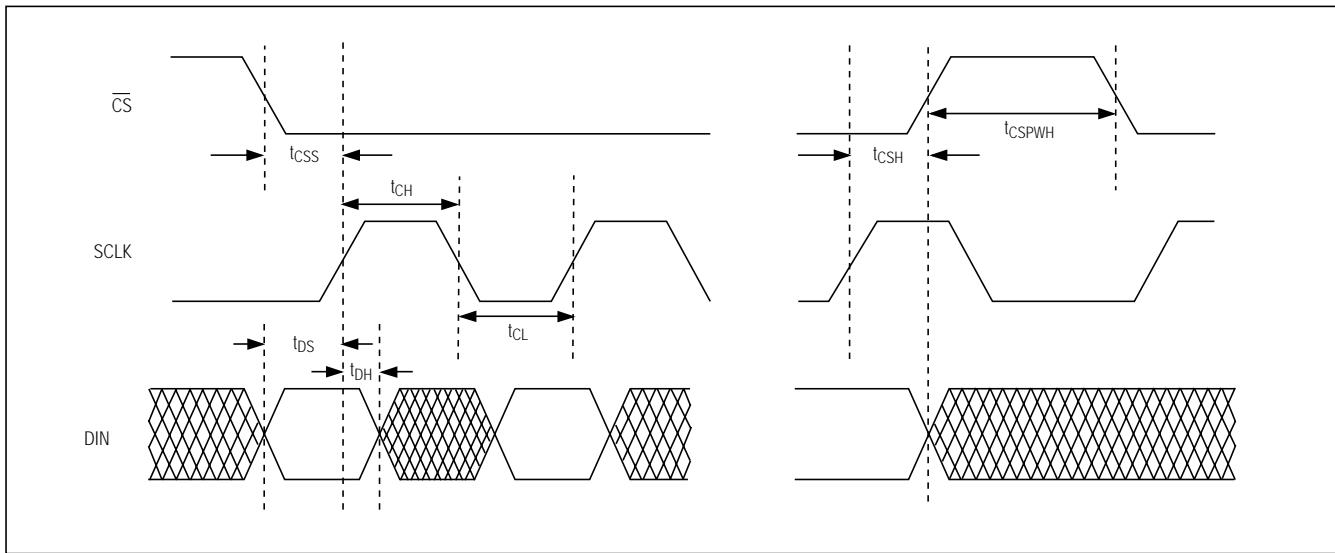

(Figure 3,  $V_{DD} = +2.7V$  to  $+5.5V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 4)

| PARAMETER                                    | SYMBOL      | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------------------------------|-------------|------------|-----|-----|-----|-------|

| <b>SERIAL INTERFACE TIMING</b>               |             |            |     |     |     |       |

| CS Fall to SCLK Rise Setup Time              | $t_{CSS}$   |            | 50  |     |     | ns    |

| SCLK Rise to $\overline{CS}$ Rise Setup Time | $t_{CSH}$   |            | 50  |     |     | ns    |

| DIN to SCLK Rise Setup Time                  | $t_{DS}$    |            | 20  |     |     | ns    |

| DIN to SCLK Rise Hold Time                   | $t_{DH}$    |            | 20  |     |     | ns    |

| SCLK Pulse Width High                        | $t_{CH}$    |            | 20  |     |     | ns    |

| SCLK Pulse Width Low                         | $t_{CL}$    |            | 20  |     |     | ns    |

| $\overline{CS}$ Pulse Width High             | $t_{CSPWH}$ |            | 50  |     |     | ns    |

**Note 1:** The outputs may be shorted to  $V_{DD}$  or GND if the package power dissipation is not exceeded. Typical short-circuit current to GND is 70mA.

**Note 2:** Reduced digital code range (code 24 through code 232) is due to swing limitations of the output amplifiers. See *Typical Operating Characteristics*.

**Note 3:** Reference input resistance is code-dependent. The lowest input resistance occurs at code 55hex. See the *Reference Input* section.

**Note 4:** Guaranteed by design. Not production tested.

MAX5223

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

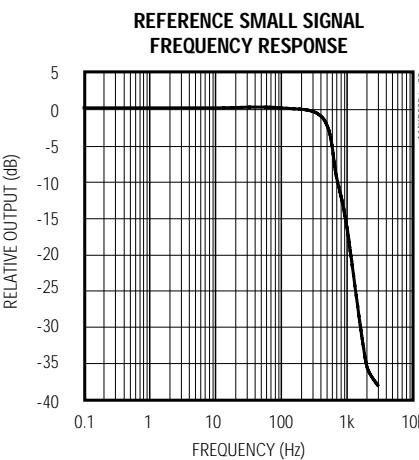

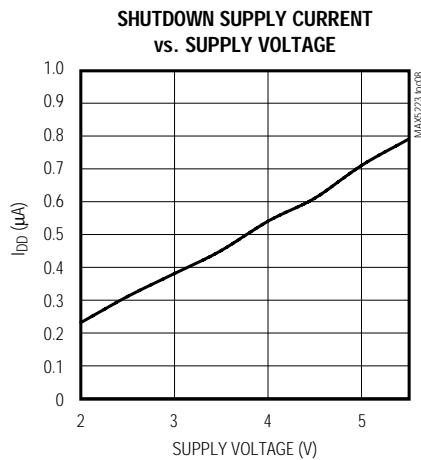

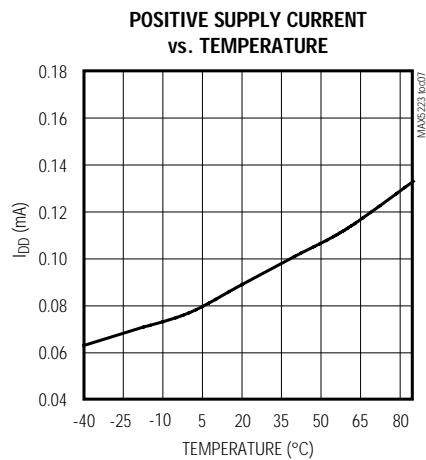

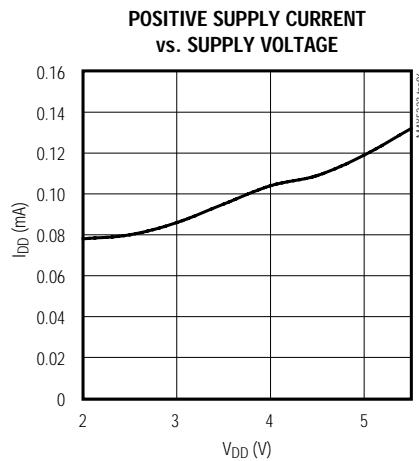

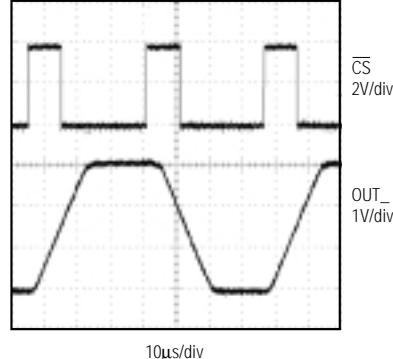

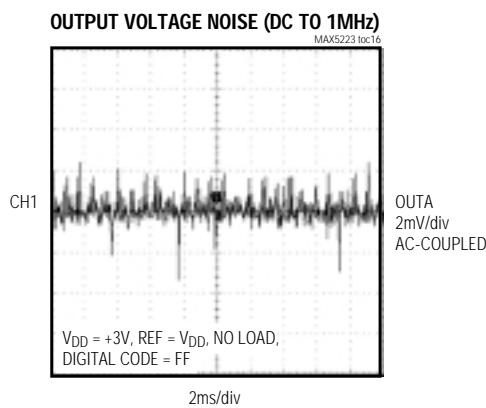

## Typical Operating Characteristics

( $V_{DD} = +3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

MAX5223

## Typical Operating Characteristics (continued)

( $V_{DD} = +3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

### LARGE-SIGNAL OUTPUT STEP RESPONSE

MAX5223 toc10

$V_{REF} = V_{DD} = +3V$

$R_L = 10k\Omega$ ,  $C_L = 100pF$

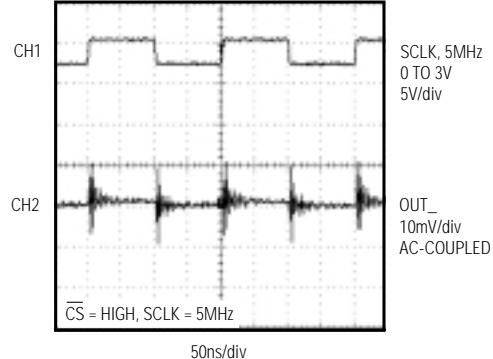

### CLOCK FEEDTHROUGH

MAX5223 toc11

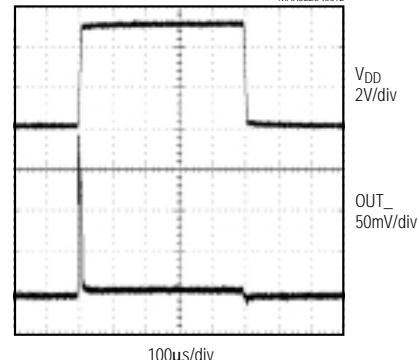

### POWER-UP OUTPUT GLITCH

MAX5223 toc12

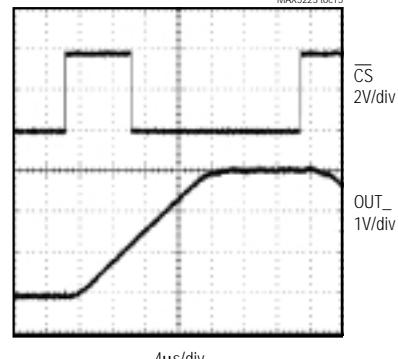

### NEGATIVE SETTLING TIME

MAX5223 toc14

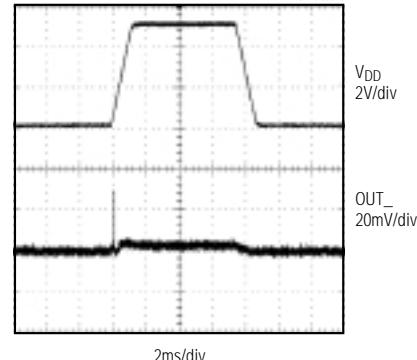

### POWER-UP OUTPUT GLITCH

MAX5223 toc13

### POSITIVE SETTLING TIME

MAX5223 toc15

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

## Typical Operating Characteristics (continued)

( $V_{DD} = +3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

## Pin Description

| PIN | NAME            | FUNCTION                                                                                                                                                      |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | $\overline{CS}$ | Chip Select. Active-Low. Enables data to be shifted into the 16-bit shift register. Programming commands are executed at the rising edge of $\overline{CS}$ . |

| 2   | GND             | Ground                                                                                                                                                        |

| 3   | $V_{DD}$        | Positive Power Supply (+2.7V to +5.5V). Bypass with 0.22 $\mu$ F to GND.                                                                                      |

| 4   | SCLK            | Serial Clock Input                                                                                                                                            |

| 5   | OUTA            | DAC A Output Voltage (Buffered)                                                                                                                               |

| 6   | OUTB            | DAC B Output Voltage (Buffered)                                                                                                                               |

| 7   | REF             | Reference Input for DAC A and DAC B (Optional: Bypass with 0.1 $\mu$ F to GND)                                                                                |

| 8   | DIN             | Serial Data Input of the 16-Bit Shift Register. Data is clocked into the register on the rising edge of SCLK.                                                 |

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

## Detailed Description

### Analog Section

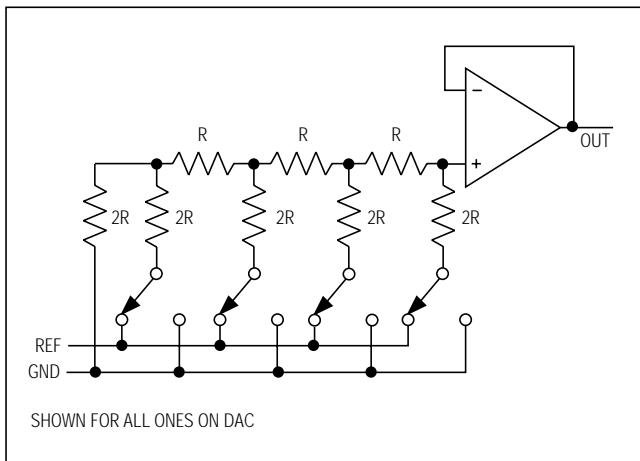

The MAX5223 contains two 8-bit, voltage output DACs. The DACs are "inverted" R-2R ladder networks. They use complementary switches that convert 8-bit digital inputs into equivalent analog output voltages in proportion to the applied reference voltage.

The MAX5223 has one reference input that is shared by DAC A and DAC B. The device includes output buffer amplifiers for both DACs and input logic for simple microprocessor ( $\mu$ P) and CMOS interfaces. The power supply range is from +5.5V down to +2.7V.

### Reference Input and DAC Output Range

The voltage at REF sets the full-scale output of the DACs. The input impedance of the REF input is code-dependent. The lowest value, approximately  $8k\Omega$ , occurs when the input code is 01010101 (55hex). The typical value of  $50M\Omega$  occurs when the input code is zero.

In shutdown mode, the selected DAC output is set to zero, while the value stored in the DAC register remains unchanged. This removes the load from the reference input to save power. Bringing the MAX5223 out of shutdown mode restores the DAC output voltage. Since the input resistance at REF is code-dependent, the DAC's reference source should have an output impedance of no more than  $5\Omega$  to meet accuracy specifications and to avoid crosstalk. The input capacitance at the REF

pin is also code dependent and typically does not exceed  $25pF$ .

The reference voltage on REF can range anywhere from GND to  $V_{DD}$ . See the *Output Buffer Amplifier* section for more information. Figure 1 is the DAC simplified circuit diagram.

### Output Buffer Amplifiers

DAC A and DAC B voltage outputs are internally buffered. The buffer amplifiers have a Rail-to-Rail<sup>®</sup> (GND to  $V_{DD}$ ) output voltage range.

Both DAC output amplifiers can source and sink up to 1mA of current. The amplifiers are unity-gain stable with a capacitive load of  $100pF$  or smaller. The slew rate is typically  $0.15V/\mu s$ .

### Shutdown Mode

When programmed to shutdown mode, the outputs of DAC A and DAC B are passively pulled to GND with a series  $5k\Omega$  resistor. In shutdown mode, the REF input is high impedance ( $50M\Omega$  typ) to conserve current drain from the system reference; therefore, the system reference does not have to be powered down.

Coming out of shutdown, the DAC outputs return to the values kept in the registers. The recovery time is equivalent to the DAC settling time.

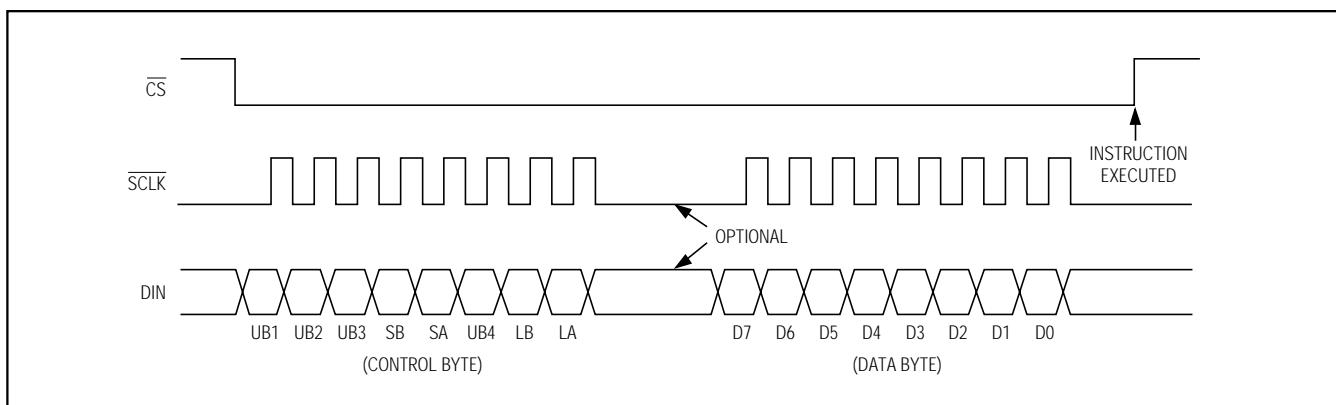

### Serial Interface

An active low chip select ( $\overline{CS}$ ) enables the shift register to receive data from the serial data input. Data is clocked into the shift register on every rising edge of the serial clock signal (SCLK). The clock frequency can be as high as 25MHz.

Data is sent by the most significant bit (MSB) first and can be transmitted in one 16-bit word. The write cycle can be segmented when  $\overline{CS}$  is kept active (low) to allow, for example, two 8-bit wide transfers. After clocking all 16 bits into the input shift register, the rising edge of  $\overline{CS}$  updates the DAC outputs and the shutdown status. DACs cannot be simultaneously updated to different digital values because of their single buffered structure.

### Serial Input Data Format and Control Codes

Table 1 lists the serial input data format and Table 2 lists the programming commands. The 16-bit input word consists of an 8-bit control byte and an 8-bit data byte. The 8-bit control byte is not decoded internally. Every control bit performs one function. Data is clocked

Figure 1. DAC Simplified Circuit Diagram

<sup>®</sup>Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

MAX5223

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

in starting with UB1 (uncommitted bit), followed by the remaining control bits and the data byte. The least significant bit (LSB) of the data byte (D0) is the last bit clocked into the shift register (Figure 2).

Table 3 is an example of a 16-bit input word. It performs the following functions:

- 80 hex (128 decimal) loaded into DAC registers A and B.

- DAC A and DAC B are active.

Table 4 shows code examples and how to calculate their corresponding outputs.

**Table 1. Input Shift Register**

| DATA BITS    | D0*   | DAC Data Bit 0 (LSB)        |

|--------------|-------|-----------------------------|

| CONTROL BITS | D1    | DAC Data Bit 1              |

| UB4          | D2    | DAC Data Bit 2              |

| SA           | D3    | DAC Data Bit 3              |

| SB           | D4    | DAC Data Bit 4              |

| UB3          | D5    | DAC Data Bit 5              |

| UB2          | D6    | DAC Data Bit 6              |

| UB1**        | D7    | DAC Data Bit 7 (MSB)        |

| LA           | LA    | Load Reg DAC A, Active-High |

| LB           | LB    | Load Reg DAC B, Active-High |

|              | UB4   | Uncommitted Bit 4           |

|              | SA    | Shutdown, Active-High       |

|              | SB    | Shutdown, Active-High       |

|              | UB3   | Uncommitted Bit 3           |

|              | UB2   | Uncommitted Bit 2           |

|              | UB1** | Uncommitted Bit 1           |

\*Clocked in last

\*\*Clocked in first

Figure 2. 3-Wire Serial-Interface Timing Diagram

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

MAX5223

**Table 2. Serial-Interface Programming Commands**

| CONTROL |     |     |    |    |     |    |    |                | DATA |    |    |    |    |    |           |                               | FUNCTION                |  |

|---------|-----|-----|----|----|-----|----|----|----------------|------|----|----|----|----|----|-----------|-------------------------------|-------------------------|--|

| UB1     | UB2 | UB3 | SB | SA | UB4 | LB | LA | D7<br>MSB      | D6   | D5 | D4 | D3 | D2 | D1 | D0<br>LSB |                               |                         |  |

| X       | X   | 1   | *  | *  | 0   | 0  | 0  | X              | X    | X  | X  | X  | X  | X  | X         | No Operation to DAC Registers |                         |  |

| X       | X   | 1   | *  | *  | 0   | 0  | 0  |                |      |    |    |    |    |    |           |                               | Unassigned Command      |  |

| X       | X   | 1   | *  | *  | 0   | 1  | 0  | 8-Bit DAC Data |      |    |    |    |    |    |           |                               | Load Register to DAC B  |  |

| X       | X   | 1   | *  | *  | 0   | 0  | 1  | 8-Bit DAC Data |      |    |    |    |    |    |           |                               | Load Register to DAC A  |  |

| X       | X   | 1   | *  | *  | 0   | 1  | 1  | 8-Bit DAC Data |      |    |    |    |    |    |           |                               | Load Both DAC Registers |  |

| X       | X   | 1   | 0  | 0  | 0   | *  | *  | X              | X    | X  | X  | X  | X  | X  | X         | All DACs Active               |                         |  |

| X       | X   | 1   | 0  | 0  | 0   | *  | *  | X              | X    | X  | X  | X  | X  | X  | X         | Unassigned Command            |                         |  |

| X       | X   | 1   | 1  | 0  | 0   | *  | *  | X              | X    | X  | X  | X  | X  | X  | X         | Shutdown                      |                         |  |

| X       | X   | 1   | 0  | 1  | 0   | *  | *  | X              | X    | X  | X  | X  | X  | X  | X         | Shutdown                      |                         |  |

| X       | X   | 1   | 1  | 1  | 0   | *  | *  | X              | X    | X  | X  | X  | X  | X  | X         | Shutdown                      |                         |  |

X = Don't care.

\* = Not shown, for the sake of clarity. The functions of loading and shutting down the DACs and programming the logic can be combined in a single command.

**Table 3. Example of a 16-Bit Input Word**

| LOADED<br>IN FIRST |     |     |    |    |     |    |    |    |    |    |    | LOADED<br>IN LAST |    |    |    |  |  |  |

|--------------------|-----|-----|----|----|-----|----|----|----|----|----|----|-------------------|----|----|----|--|--|--|

| UB1                | UB2 | UB3 | SB | SA | UB4 | LB | LA | D7 | D6 | D5 | D4 | D3                | D2 | D1 | D0 |  |  |  |

| X                  | X   | 1   | 0  | 0  | 0   | 1  | 1  | 1  | 0  | 0  | 0  | 0                 | 0  | 0  | 0  |  |  |  |

### Digital Inputs

The digital inputs are compatible with CMOS logic. Supply current increases slightly when toggling the logic inputs through the transition zone between  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

### Microprocessor Interfacing

The MAX5223 serial interface is compatible with MICROWIRE, SPI, and QSPI. For SPI, clear the CPOL and CPHA bits (CPOL = 0 and CPHA = 0). CPOL = 0 sets the inactive clock state to zero, and CPHA = 0

changes data at the falling edge of SCLK. This setting allows SPI to run at full clock speeds. If a serial port is not available on your  $\mu$ P, three bits of a parallel port can be used to emulate a serial port by bit manipulation. Minimize digital feedthrough at the voltage outputs by operating the serial clock only when necessary.

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

Figure 3. Detailed Serial-Interface Timing Diagram

## Applications Information

The MAX5223 is specified for single-supply operation with  $V_{DD}$  ranging from +2.7V to +5.5V, covering all commonly used supply voltages in +3V and +5V systems.

### Initialization

An internal POR circuit forces the outputs to zero scale and initializes all internal registers to zero. Perform an initial write operation to set the outputs to the desired voltage at power-up.

### Power-Supply and Ground Management

GND should be connected to the highest quality ground available. Bypass  $V_{DD}$  with a  $0.1\mu F$  to  $0.22\mu F$  capacitor to GND. The reference input can be used without bypassing. For optimum line- and load-transient response and noise performance, bypass the reference input with  $0.1\mu F$  to  $4.7\mu F$  to GND. Careful PC board layout minimizes crosstalk among DAC outputs, the reference, and digital inputs. Separate analog lines with ground traces between them. Make sure that high-frequency digital lines are not routed in parallel to analog lines.

## Chip Information

TRANSISTOR COUNT: 1480

PROCESS TECHNOLOGY: BICMOS

Table 4. Code Table

| DAC CONTENTS |    |    |    |    |    |    |    |                                                              | ANALOG OUTPUT |

|--------------|----|----|----|----|----|----|----|--------------------------------------------------------------|---------------|

| D7           | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                                                              |               |

| 1            | 1  | 1  | 1  | 1  | 1  | 1  | 1  | $+REF \times \left(\frac{255}{256}\right)$                   |               |

| 1            | 0  | 0  | 0  | 0  | 0  | 0  | 1  | $+REF \times \left(\frac{129}{256}\right)$                   |               |

| 1            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | $+REF \times \left(\frac{128}{256}\right) = + \frac{REF}{2}$ |               |

| 0            | 1  | 1  | 1  | 1  | 1  | 1  | 1  | $+REF \times \left(\frac{127}{256}\right)$                   |               |

| 0            | 0  | 0  | 0  | 0  | 0  | 0  | 1  | $+REF \times \left(\frac{1}{256}\right)$                     |               |

| 0            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0V                                                           |               |

**Note:**

$$1\text{LSB} = \text{REF} \times 2^{-8} = \text{REF} \times \left(\frac{1}{256}\right)$$

$$\text{ANALOG OUTPUT} = \text{REF} \times \left(\frac{D}{256}\right) \text{ where D = decimal value of digital input}$$

# Low-Power, Dual, 8-Bit, Voltage Output Serial DAC in 8-Pin SOT23

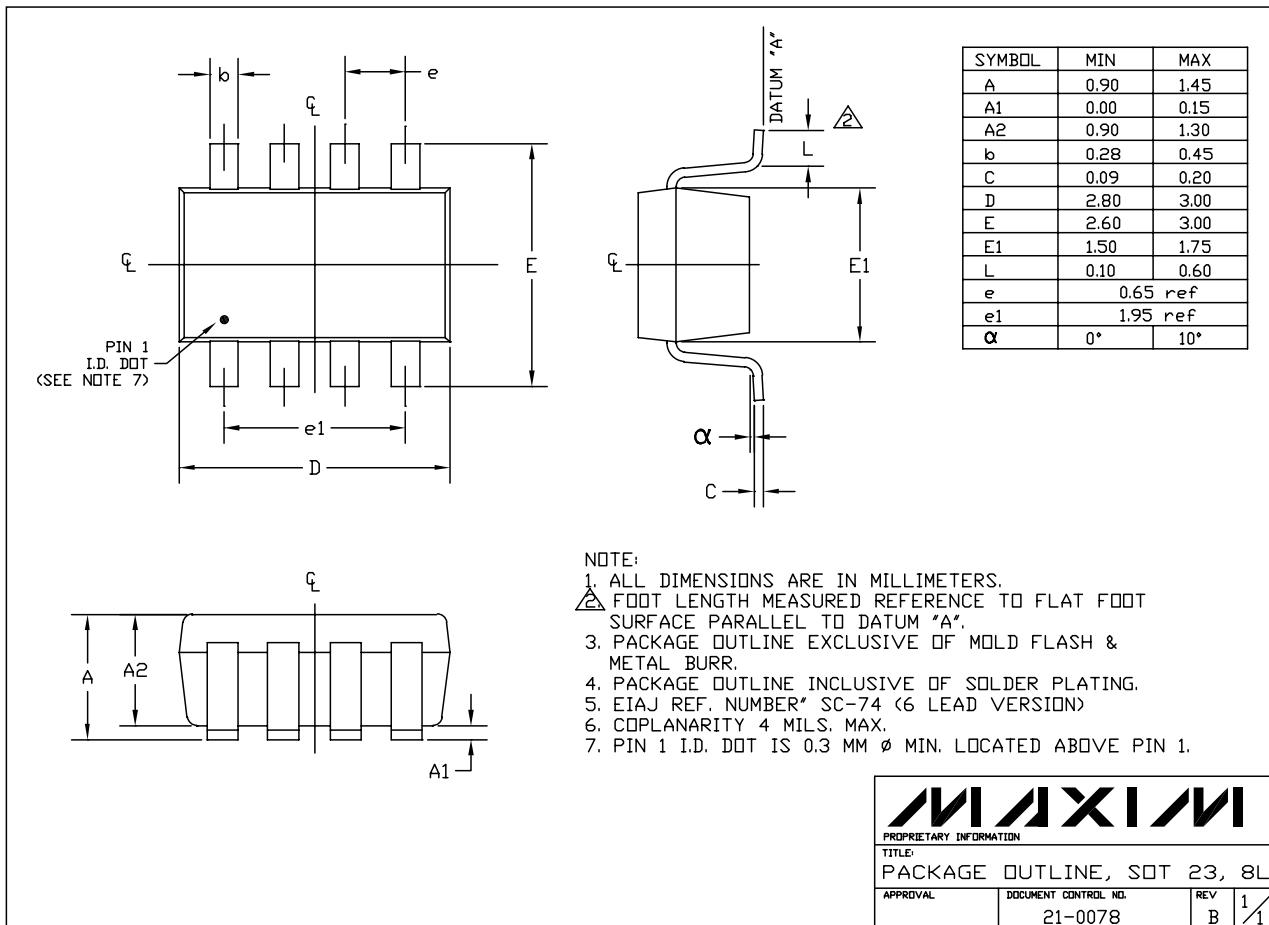

## Package Information

MAX5223

SOT23\_8L.EPS

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 11